A EVOLUÇÃO DAS SDRAM

EVOLUÇÃO GENÉRICA

Gráfico comparativo da relação de frequências nos diferentes tipos de memorias SDRAM

Durante a evolução da SDRAM foi decrescendo a dimensão dos transístores e foram-se conseguindo menores voltagens de trabalho.

Em consequência conseguiram-se aumentar as frequências de vibração disponíveis nos Dies, sem que isso provocasse o seu sobreaquecimento e sem que houvesse lugar a transmissão de ruído.

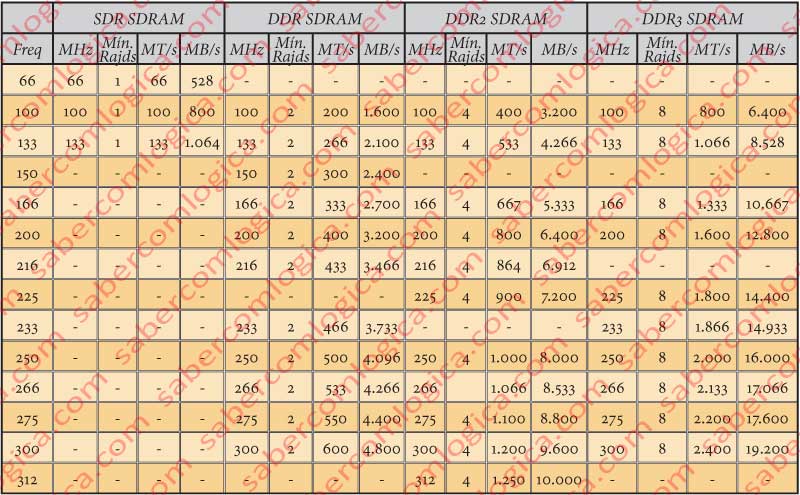

Juntamos na Figura 49 uma tabela com a evolução das taxas de transferência comparadas com a evolução das frequências de clock nas memórias SDRAM.

Podemos verificar que da SDR para a DDR houve uma substancial evolução na gama de taxas de transferência dos módulos. Já da DDR para as DDR2 ou DDR3 as gamas de frequências permaneceram praticamente inalteradas.

Os valores das latências, os tempos necessários para completar cada fase da operação de leitura ou escrita que resultam comportamento interno das células da memória, tiveram reduções da ordem de uns escassos 50% durante toda esta evolução, havendo mesmo tempos que mal atingiram os 20%.

Foi nas taxas de transferência de dados entre o módulo e o CM que a evolução das SDRAM foi mais notória. E estas medem-se em T/s e não em Mhz.

Quando se anuncia que um módulo DDR3 tem frequências de 2,4 GHz está-se a prestar uma informação deturpada. Efetivamente o módulo tem 300 MHz de frequência interna de vibração do clock, a que correspondem 2,4 GT/s, ou seja, 2,4 mil milhões de transferências por segundo.

DDR

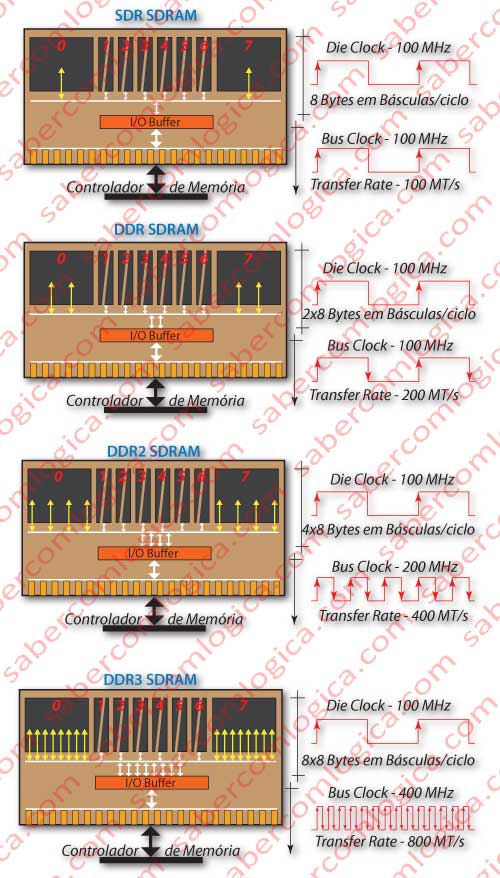

DDR SDRAM (Double Data Rate Synchronous Dinamic Random Access Memory) ou Memória Dinâmica de Acesso Aleatório com Dupla Taxa de Transferência de Dados, vulgo DDR, é uma evolução da SDRAM que consta do aproveitamento de ambos os flancos do clock para ler/escrever dados consecutivos em duas rajadas.

Os buffers de saída são diferentes, pois em lugar de serem de 1 bit serão de 2 bits, pois em cada ciclo de clock do Die de memória passaremos a ter disponíveis dois bits em cada buffer.

Portanto, nas DDR, para a mesma frequência dos Die duplica a taxa de transferência de dados.

DDR2

DDR2, é uma evolução das memórias DDR em que o número de dados lidos em cada ciclo de clock do Die volta a duplicar.

Embora este tema não tenha sido abordado, é possível iniciar uma leitura num Banco refrescado duma SDR SDRAM logo após a conclusão da leitura em rajada numa linha de outro Banco, desde que este se encontre refrescado, diminuindo assim o valor da latência de uma leitura iniciada de fresco.

A expansão do número de Bancos (de 4 para 8) nas DDR2 aumenta a possibilidade de ter sempre um Banco refrescado após uma leitura em rajada, gerando menos latência na mudança entre Bancos, pelos métodos e técnicas que vimos atrás para as SDRAM, para além de permitir o aumento de capacidade dos Die.

Nas DDR 2, por técnicas de pipeline, a cada meio ciclo de clock do Die, começa uma leitura sequencial em rajada para esta memória. Para este efeito cria um novo clock interno a partir do clock do Die, podendo assim iniciar rajadas a meio do anterior clock do Die.

Os buffers de saída passam a ter 4 bits de profundidade em lugar de 2, pois passamos a ter 4 bits por buffer em cada ciclo de clock do Die.

Portanto, nas DDR2, para a mesma frequência dos Die quadruplica a taxa de transferência de dados.

DDR3

DDR3, é também ela uma evolução da DDR2, onde mais uma vez se duplica o número de dados lido no mesmo ciclo de clock do Die, conseguida por técnicas mais elaboradas de pipeline que permitem efetuar 8 leituras sequenciais em rajada dentro do mesmo ciclo de clock do Die.

Para isso as memórias vão ter um segundo clock interno que é 1/4 do clock do Die e que vai servir para dar início a cada uma das leituras correspondentes a cada uma das rajadas.

Nas DDR3 os buffers de saída, em lugar de serem de 4 bits passam a ter 8 bits de profundidade em lugar de 4, pois passamos a ter 8 bits, ou seja 1 byte, por ciclo de clock em cada Buffer.

Portanto, nas DDR3, para a mesma frequência dos Die octuplica a taxa de transferência de dados.

Tabela da evolução das taxas de transferências nas memórias SDRAM

DDR4

DDR4 já não vai ser uma simples evolução das DDR3, como esta e as anteriores foram em relação às suas antecessoras. Para além de mais uma vez duplicar a taxa de transferência de dados, estes novos módulos vão usar uma nova arquitetura de ligação ao controlador.

A atual opção de duplo ou triplo canal com vários módulos por canal, vai ser substituída por uma ligação ponto a ponto entre o controlador e cada módulo independentemente, um só por canal.

Isto poderá fazer pressupor que o paralelismo passe do barramento para o CM, como aconteceu entre o PCI e o PCIe. A partir daqui o céu é o limite para a imaginação.

O número de Bancos irá aumentar para 16, permitindo assim mais linhas refrescadas após cada leitura, por forma a poder iniciar mais leituras em cada ciclo de clock do Die. Aumentará também a capacidade dos Die.

A voltagem será ligeiramente reduzida, permitindo ligeiros aumentos de frequência de clock. O tempo de duração de cada leitura também só terá pequenas reduções nas latências. Mas mesmo assim passará a duplicar a taxa de transferência da DDR3.

A comercialização destas memórias está prevista para 2013 e a sua utilização pelos principais fabricantes de Chips de CPU para 2014, na Intel com a arquitetura Haswell-E e na AMD com a arquitetura Hierofalcon SOC.