Excess in a sum

When we executed the operation 65-37 we ignored the last carry out of the circuit, which had the value 1. And we ignored it just because the circuit didn’t have enough bits to represent it.

Ignoring that carry, normally we would be incurring in an error, as all bits are significant when part of a number. But we didn’t, because as we could see, the result was the one we wanted to be!

Ok. And we are very happy, because we already know that when subtracting 37 from 65 we can ignore the last carry out. Just as a curiosity: If we subtract 38 from 65 how will it be?

It’s in this kind of situations that the computer is extremely demanding. We have to teach it accurately how it acts in all possible situations, finding a formula that establishes a logical connection to a standard behavior. In mathematics and logic we can only face two possible circumstances:

- We understand the reason of a procedure and thus we can find the formula that explains its behavior in all the possible situations.

- We don’t understand the reason of a procedure and therefore we can not explain it to ourselves. Far less to the computer.

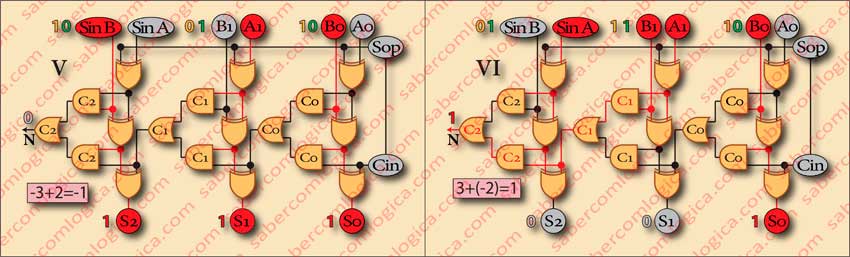

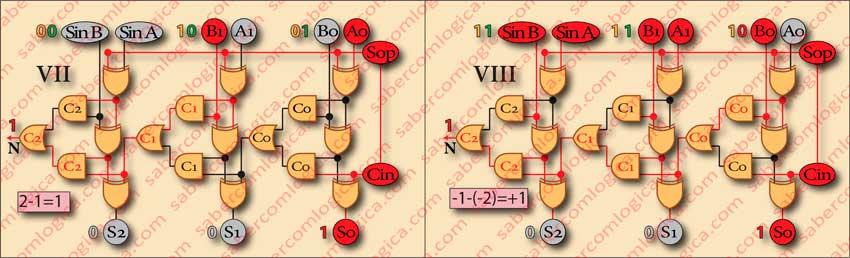

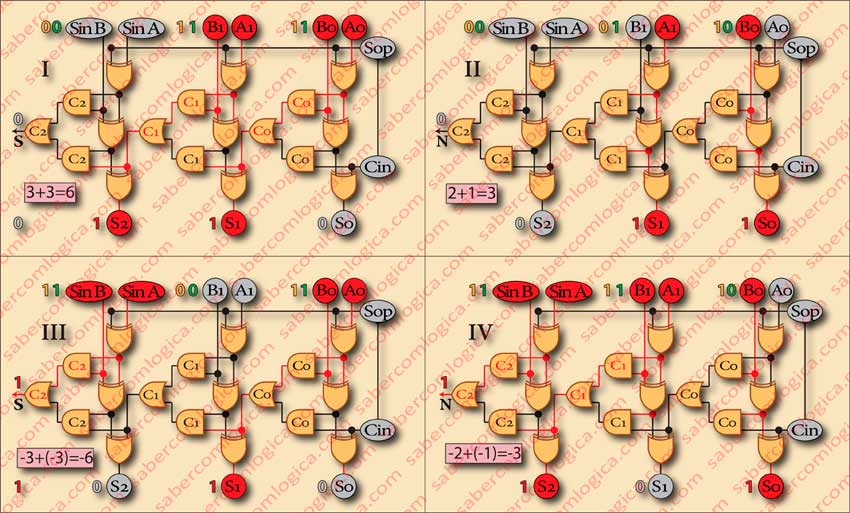

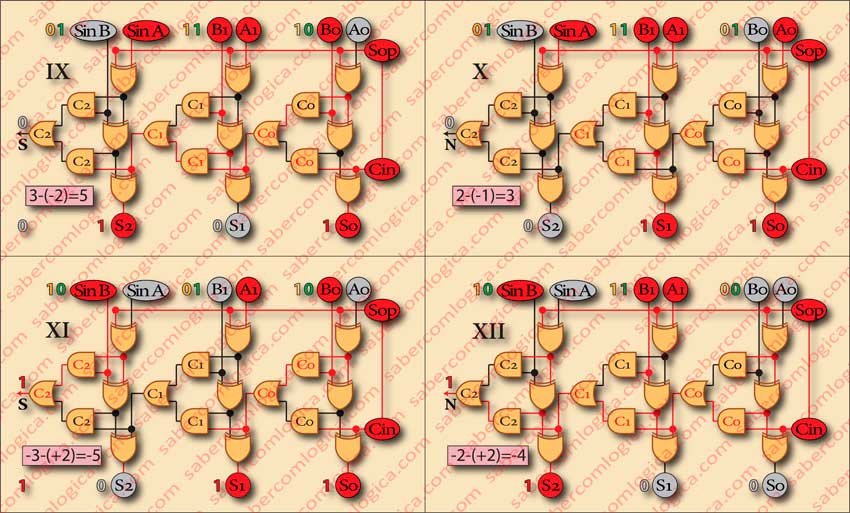

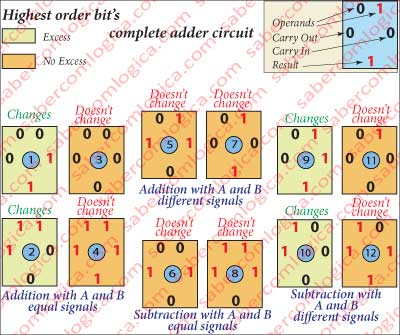

This was the reason that took us to create the 12 frames of Figure 1 representing several operations with a 3 bit adder circuit , being the order 2 bit the sign. In these frames we analyze the possible combinations of the operands, their signs and type of operations in order to find a common behavior for the value of Excess. We have created another frame in Figure 2, representing a summary of the first 12 frames in what concerns the behavior of the highest order bit compared with the operands, the result and both carry in (Ci) and carry out (Co).

We will verify that the Excess is not mandatorily significant when Co is 1 and insignificant when Co is 0.

Everything that we are going to analyze refers to numbers represented in two’s complement, thus signed numbers, where the highest order bit is always significant, because it represents the sign. For unsigned numbers this question is meaningless, as with these either the result Carries 1 and is significant or it Carries nothing and is irrelevant, just as it goes with us, in our decimal system.

1. When the operands of an addition have different signs there’s no room for Excess.

There’s no need of any frames to get to this conclusion. If the operands have different signs, the result of their addition will always be smaller than the greater of them, thus being representable with the same number of bits used for the operands. Any carry out from the circuit, 1 or 0, will be irrelevant. We can say with all the property that in this situation there’s no room for Excess. Nevertheless we can see this situation represented in the Frames V and VI where we can verify the behavior of the logical circuit and even in one of them the existence of a Co with the value 1.

As we said, Co=1 doesn’t mandatorily mean the existence of Excess.

2. When the operands of a subtraction have equal signs there’s no room for Excess.

This statement is identical to the first one. We only used a different way to say it.

-a -(-b) = -a + b

The result will always be smaller than the greater operand, thus being representable with the same number of bits used for the operands. We can see this statement graphically represented in the Frames VII and VIII where we can see the logical circuit behavior and again the existence of a Co with the value 1 in one of them.

Once again Co=1 doesn’t mandatorily mean the existence of Excess.

3. When the operands of an addition have equal signs and the result sign is different from the operands sign, then we will have Excess.

(+a)+(+b) = a+b

(-a)+(-b) = -a-b

This situation happens when the operations result is not representable with the same number of bits used for the operands. Thus, the most significant bit of the unsigned part of the result is placed in the order bit where the operands sign was and the result sign is transported by the Co. If the operands have 3 bits in two’s complement, the value being analyzed is the order 2 bit.

It’s clear that the sum of two numbers with the same sign has to be a number with the same sign. And we don’t need any graphic to conclude it. Thus, if the sign changes its value its because a significant bit replaced it.

Why does it change? The new bit can have the same value as the sign. After all the sign is a bit of value 1 or 0.

If both the operands are positive (0), the first bit in a new order resulting from their sum will be 1, as that’s how positive numbers increase. So, the sign (always 0) will be replaced by the new order bit of increasing positive numbers (always 1).

Thus, for the last bit adder Ci is 1 and Co is 0, whenever there’s Excess.

As we said, we can have room for Excess even when Co is 0.

If both the operands are negative (1), the first bit in a new order resulting from their sum will be 0, as that’s how negative numbers decrease. So, the sign (always 1) will be replaced by the new order bit of decreasing negative numbers (always 1).

Thus, for the last bit adder Ci is 0 and Co is 1, whenever there’s Excess.

The situations now described can be viewed in Frames I to IV of Figure 1 as in the little frames of Figure 2.

4. When the operands of a subtraction have different signs and the result sign is different from the first operand sign, then we will have Excess.

(+a)-(-b) = a +b

(-a)-(+b) = -a- b

This statement is identical to the previous one, only differing in the way its is stated. Subtracting a negative number its the same as adding a positive one. Let’s verify it in Frames IX a XII of Figure 1. We just want to emphasize now the reference we made to the first operand’s sign:

Here the difference of signs is referred exclusively to the firs operand.

Conclusion

Actually, if we look to the frames where the Excess situations are represented (in these frames the last Co as written below it the letter S), Frames I, III, IX and XI, we can verify that the result of the operation, if expressed only by 3 bits as the operands, will be wrong. But if we add a 4th bit to absorb the Co value, then the result will be correct.

Concluding: We can verify Excess situations only when the Co of the highest order bit adder transports the sign’s value, as its value in the previous order was replaced by a significative bit for the number’s unsigned part.

Now, how can we teach this to the computer?

Let’s look to the 8 little frames in Figure 2 where the situations in which there is and there isn’t room for Excess are identified by different colors, according with the analysis that we have just done. The frames symbolize the adder circuit of the highest order bit.

When it’s written “Changes” it’s because the Ci and Co of that circuit are different. When it’s written “Doesn’t Change” it’s because the Ci and Co are equal.

Regarding these considerations we can verify that whenever there is Excess, Ci and Co of the last adder are different and whenever there isn’t Excess, Ci and Co of the last adder are equal. We have found the logical relationship that rules this type of event in any situation. Now we can teach the computer, just telling it that:

If the last two Co are different there is Excess. If the last two Co are equal there isn’t Excess. Just remember that the Ci of a bit adder circuit is the Co of the previous order one. Thus the Ci of the highest order bit adder is the Co of its previous order bit adder. So, we can say that there’s room for excess when the Co and the Ci of the highest order bit adder are different and that there’s no room for excess when the Co and the Ci of the highest order bit adder are equal.

But this statement is written in English, and the computer says it doesn’t understand it. We have to translate it. And that as to be done by introducing in the circuit something that tells the computer about the relation of those two last Co. And that only can be done with a 1 or a 0.

Let’s see: Both different its true and both equal its false. Where did we hear that?

This statement is identical to the XOR logical gate truth table.

That’s it!

So, we connect those two last Co to a XOR logical gate ant it’s output will tell the computer if there’s room for Excess or not, as its value is 1 or 0.

The excess detection is very important, because its existence together with the impossibility of extending the circuit number of bits implies an error, producing an incorrect result for the operation. Once detected and informed the Operating System, if necessary it stops the program with an error message, in order to avoid the error propagation. The Operating System is something about what we will speak latter in a future Chapter. Windows, iOS and Linux are examples of Operating Systems.

The emphasis we have given to this theme is due to the fact that the purpose of this work is the exact opposite of the introduction of axioms, or of unexplained statements.

The names of things can be memorized, but the logic who’s behind certain procedures has to be understood. We had to demonstrate the reason why ignoring a Carry Out bit in a two’s complement operations is not mandatorily a mistake.

We hope we have succeeded.