PRIMARY MEMORY

INTRODUCTION

CPU works in a permanent cycle of search, decode and execute. It is precisely in the Primary Memory that CPU searches, in the address indicated by the program counter. Hence the importance of memory, reflecting a better or worse performance of CPU.

The ideal working environment would be the existence of an enormous amount of memory working at a frequency equal to CPU. But this ideal is just that. Economically and physically impossible.

Hence the existence of several hierarchical levels of memory, with different costs, capacities and frequencies of access cycles. And so, with a great deal of imagination, logical reasoning and investigation, that got a lot closer to the ideal, economically and physically sustainable.

Computer science has always evolved based on these assumptions. It’s the intelligence and logical thinking ability that makes developers create programs that exceed the hardware capabilities. It’s the intelligence and integration of logical reasoning of hardware technicians that makes the hardware evolve beyond the needs of developers. And so on.

Being the Primary Memory the one who sustains the operation of all other levels of memory (it feeds cache memory and works as an HDD cache), we decided to start our memory analysis by it. Once properly understood its concept of operation, we will move on to the analysis of the remaining levels and their interconnection.

DYNAMIC MEMORY

The primary memory of a computer is composed of a set of billions of cells that contain the smallest information unit, the bit, with its load of logical 0 or 1.

Imagine those cells as rooms where each one of our messengers lives, waiting to be called by someone who needs the valuable information they contain. These rooms are arranged in buildings, streets, neighborhoods and finally in a large city with billions of rooms.

If we need the information contained by a particular messenger, George for instance, we surely wouldn’t ask to the manager of the great city for George. Surely he would be looking at us and ask:

Where is he?

Question more than evident, for he would not look into billions of rooms to find George.

When a room for George was booked, an address in that great city was given to us, referring the neighborhood, the street, the building and the room where it is. In short, we were given George’s address in the big city. And only through that address we will be able to find George. If we lose his address, we lose the chance to find George again and the information he has will be definitely lost .

This is the concept that was missing for the definition of Primary Memory: It’s where the information that the CPU uses to work is registered in places from whose addresses the CPU is previously informed of, so it can find them.

Therefore, any memory cell contains an information and a single and unique address.

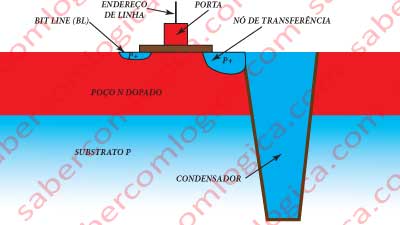

The main memory cells are of great simplicity, composed by a transistor and a capacitor which stores the voltage data, the room where our messenger lives.

But there is a little disadvantage. The capacitor, like any other, will lose the charge it contains in a short period of time, therefore having to be periodically refreshed, let’s say a few thousand times per second. It’s like a bucket that is broken and it’s slowly losing its contents. So, before it goes to an indefinite state it must be refreshed, in order that its content can always be recognized when it’s read, thus being refreshed to its original state (Figures 1, 2 and 3).

a) Um bit, ou célula de memória com carga representando o estado lógico 1. b) Um bit, ou célula de memória sem carga representando o estado 0. c) Um bit, ou célula de memória com perda de carga e a necessitar de refrescamento para ser reconhecido como representando o estado lógico 1.

Such a memory cell, loosing charge and thus having not a static behavior, is called Dynamic, thus giving rise to the name of the main memory – DRAM (Dynamic Random Access Memory) .

Why Random Access?

Because we can access any cell anywhere, without having to conform to any criteria or sequence, simply typing its address.

It’s easy! The CPU tells the Memory Controller (MC) the address where the data that it needs is, the MC will get it in that address and returns it to the CPU.

Just to understand a little better how easy it is, let’s make an analogy: Try to remember those very large Christmas trees that now all major cities exhibit in that epoch of the year.

Notice the huge amount of tiny lamps (LEDs) that light it up. They are many, even many. Now imagine a great avenue full of trees like this, loaded with those lamps. Billions of lamps.

Now, tell us what would you call the guy that requires assemblers to control each one of these lamps individually.

Crazy, surely! Only the electrical conductors necessary in order to perform this desire would certainly cover the trees and even the Avenue.

Well, the Primary Memory is just that. Billions of these small lamps (bits or memory cells) containing the information corresponding to the state of on or off, which in groups of 8 (the bytes) provide the necessary information for developing the computer’s activity. And they have to be read and written individually.

After all, it is not as easy to do as to say. Remembering the Avenue with the huge Christmas trees, will surely make easier to imagine how difficult it is forwarding a circuit for a lamp in the middle of thousands of millions of others, to power it on or off individually.

It’s not easy, not at all. But it’s possible. And after analyzing it under a simplistic perspective, its going to seem easy.

As usual, let’s start by the essential, with the possible simplicity. The complexity is the sum of many simplicities.

Let’s examine how the memory is physically organized and how it gets to each of those cells and writes or reads a value there.

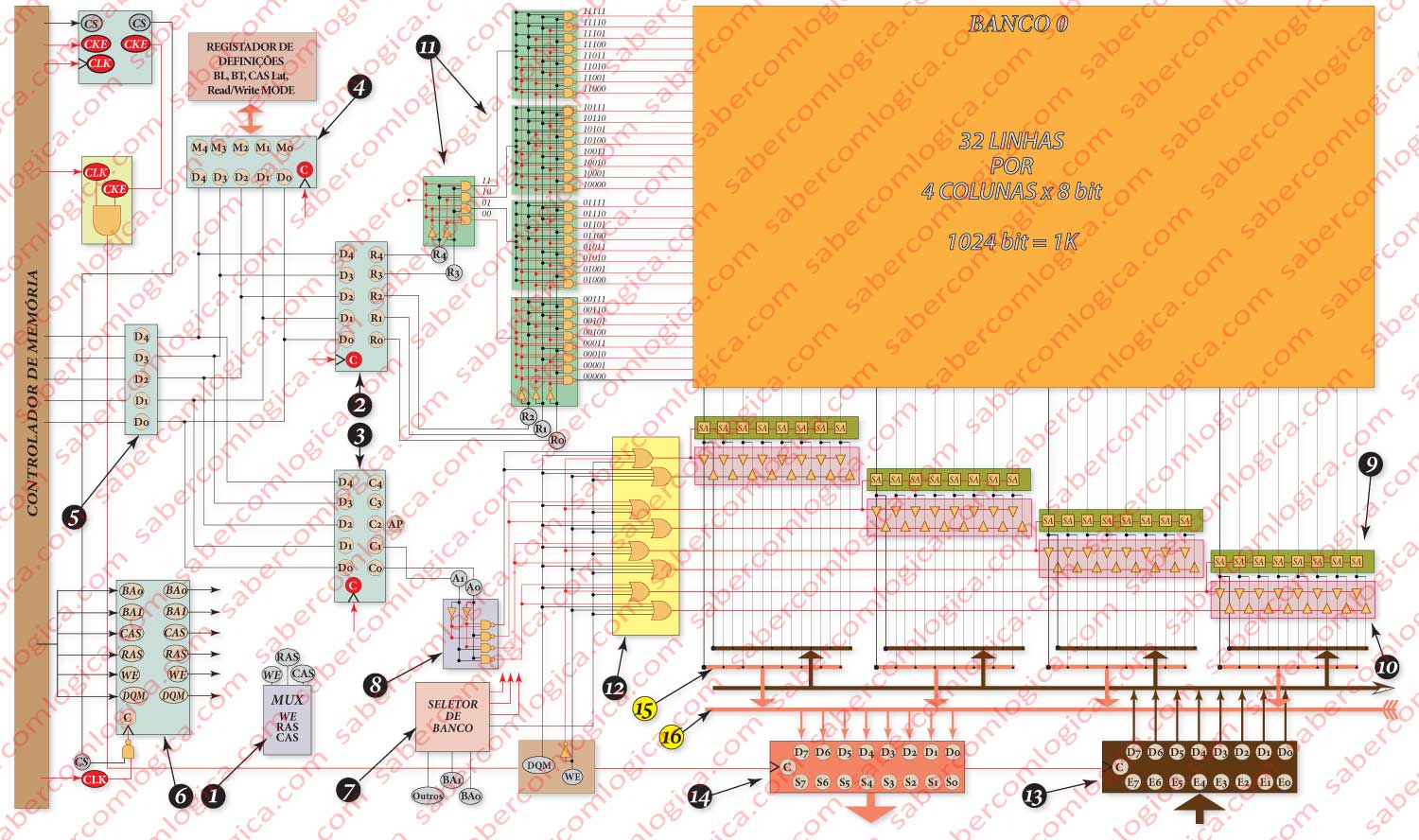

A ORGANIZAÇÃO DA MEMÓRIA

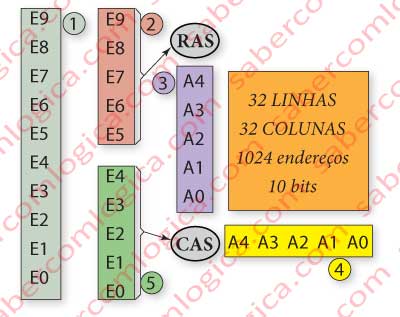

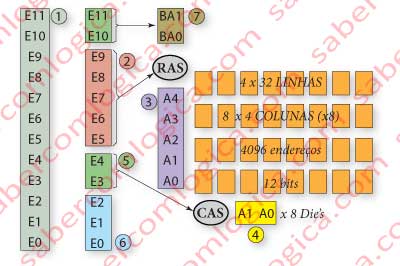

Endereçamento ao bit. 1) Endereço conforme é enviado da CPU ao controlador de Memória. 2) Parte desse endereço enviado pelo Controlador à MP com o sinal RAS. 3) Forma do endereço no registador de endereços de linha. 4)Parte do endereço enviado pelo Controlador à MP com o sinal CAS. 5) Forma do endereço no registador de endereços de coluna.

Os fabricantes de memórias, por questões ligadas à desmultiplexação mais facilitada, ao refrescamento e outras, organizam os chips de memória sob a forma de matrizes (quadros) quadradas de bits, que é, como se sabe, a menor unidade de informação. O local de armazenamento de um bit fica desde já designado como célula de memória.

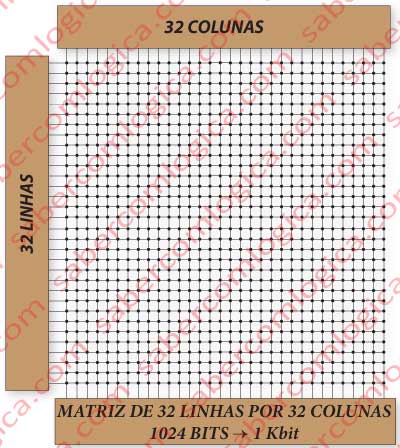

Consideremos um chip de memória com 1 Kbit, ou seja, 1.024 bits. Este encontra-se organizado sob a forma de uma matriz quadrada de 32 linhas por 32 colunas, tal como representado na Figura 5.

O Controlador de Memória (CM) é o responsável por toda a gestão da MP. É ele que traduz as instruções da CPU em instruções para a MP. O CM encontra-se localizado no Northbridge ou, nas CPU mais recentes, no próprio chip da CPU. Para já o que nos interessa do CM é a forma como ele trata dos acessos à memória.

Para aceder ao nosso chip de 1024 bits, a CPU envia um endereçamento composto por 10 bits (210=1024). O controlador desdobra esse endereço em duas partes iguais e envia-os separadamente à MP com um sinal que define ao que respeita. Ver Figura 4.

Assim, o controlador envia a metade dos bits de maior ordem junto com um sinal

Gráfico representativo da organização de um chip de memoria de 1Kb.

RAS (Row Access Strobe ou Sinal de Acesso a Linha). A MP

recebe esse endereço no registador de endereços e envia-o para o registador de endereços de linha por ação do sinal RAS. No pulso seguinte de clock o controlador envia a segunda metade do endereço, composta pelos bits de menor ordem, acompanhada pelo sinal CAS (Column Access Strobe ou Sinal de Acesso a Coluna) e a MP coloca-o no registador de endereço de coluna por ação do sinal CAS.

A divisão do endereço em duas partes, em lugar do envio do mesmo por completo, deixando à memória a sua divisão, tem a ver com a redução do número de pinos necessários, bem como com a forma de leitura e escrita para que as memórias SDRAM estão concebidas.

Já que falámos nisso, a evolução da análise da MP que vamos fazer, vai evoluir para uma memória SDRAM (Synchronous Dinamic Random Access Memory) a funcionar em módulos DIMM (Dual In-line Memory Module, ou seja, com contactos distintos de ambos os lados), vulgo “pente“.

Não se pode considerar um tipo de memória de última geração, mas as mais recentes representam evoluções desta (DDR SDRAM, DDR2 SDRAM, DDR3 SDRAM), como perceberão no final do Capítulo quando nos referirmos a elas. Mas vamos em frente.

A CPU ignora os bits ou células de memória. O elemento mais pequeno que a CPU conhece na memória é o Byte (8 bits) e é sempre por endereçamento a esse que se dirige à mesma. Portanto, os endereços de que falámos até agora não se referem a células de memória mas à posição inicial ocupada por conjuntos de 8 dessas células, o Byte.

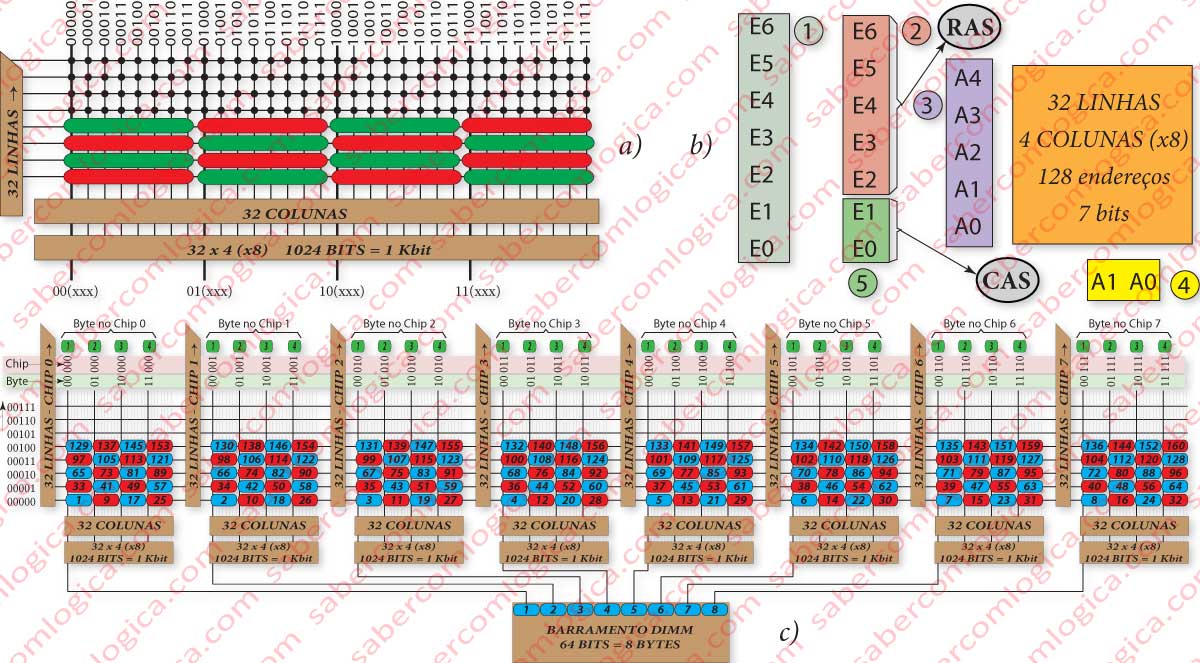

Sendo assim, a distribuição das posições de memória em termos de endereçamento passa a ter uma forma retangular, ou seja 32 linhas e 4 colunas, cada uma referente a um conjunto de 8 bits.

Temos agora para a mesma matriz, 128 posições de endereçamento, o que se consegue com 7 bits (27=128), um número ímpar que não dá para dividir por dois.

Mas não é mesmo para dividir. Os chips de memória são compostos por matrizes quadradas de bits e não de Bytes.

Como o número de posições a representar em colunas é um submúltiplo de 8, agora os bits necessários para as endereçar é reduzido de 3, os necessários para representar as 8 posições que se englobam.

a) No gráfico em cima mostra-se a nova organização da memória, estando preenchidos a vermelho e a verde os Bytes, vendo-se os bits que cada um preencheu. b) O quadro à direita mostra o endereçamento da mesma matriz, mas agora ao Byte. A legenda é idêntica à da Figura 4. Os sinais CAS, RAS são enviados pelo controlador à MP. c)No gráfico acima representasse o conjunto de 8 chips de 1Kbit que preenche o barramento de 64bits do DIMM, constituindo em conjunto 1KByte. Assim teremos que os Bytes 1 a 8 estando nos chips 0 a 7 repetidamente, por forma a representarem uma sucessão na palavra de 64 bits. Da mesma forma os bits 9 a 16 estarão na 2ª coluna de cada chip 0 a 7 e assim sucessivamente.

Analisando os quadros da Figura 6a e b, torna-se muito mais fácil de entender.

Assim sendo, as colunas necessitam apenas de 2 bits (5-3=2) para serem representadas. São 4 Bytes que, para serem selecionados, precisam de 2 bits (22=4). Como se pode bem ver na Figura 6a, dos 5 bits necessários para representar as células dos 4 Bytes, os 2 de maior ordem mantém-se constantes para cada Byte e variam de Byte para Byte, enquanto os 3 de menor ordem representam as células (bits) dentro de cada Byte, repetindo-se para cada um.

Necessitamos assim de muito poucos bits (concretamente 7) para representar os endereços da nossa pequena memória didática.

Os DIMM de que estamos a falar preenchem um barramento de 64 bits, isto é, têm 64 pinos para entrada/saída de dados que ligam a um barramento de memória que os encaminha até ao CM.

Embora nos vamos sempre referir ao Byte como unidade base de informação com que trabalhamos, não vamos esquecer que os 64 bits são o tamanho do barramento de dados de quase todos os computadores comercializados atualmente. Mesmo nos mais antigos, com palavra de 32 bits, o tamanho do barramento de dados já era de 64 bits. Um DIMM serve simultaneamente 64 linhas de dados.

Como cada chip só pode contribuir com 1 byte por cada leitura, vamos ter que juntar mais 7 chips ao primeiro, iguais a ele, por forma a que em conjunto todos debitem de cada vez 1 Byte, o que perfaz os 8 Bytes necessários ao preenchimento do barramento.

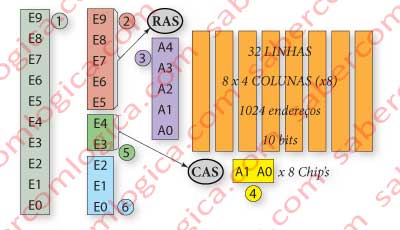

Ao colocarmos 8 chips no módulo DIMM, revertemos a anterior retirada de bits de endereço, quando juntámos os 8 bits em 1 Byte. Assim, o endereçamento das colunas volta a necessitar de 5 bits para ser representado.

Agora passámos a ter 8 x 128 posições de memória a endereçar, ou seja, novamente as 1024 posições. Só que em Bytes. Voltamos portanto a ter o mesmo número de bits de endereçamento em linhas e colunas.

Se esta afirmação, para a CPU é verdadeira, já o mesmo não se pode dizer em termos de CM. Este precisa de controlar a memória por forma a que tenha disponíveis em simultâneo 64 bits (8 Bytes) na saída do módulo de memória.

Embora a CPU possa solicitar à memória posições de outra dimensão, como um Byte, uma Word (16 bits), uma DoubleWord (32 bits) ou uma QuadWord (64 bits), porque entre a MP e a CPU está a Memória Cache, aquela a que a CPU acede, vamos admitir que o barramento de dados transporta até aí os 64 bits. Portanto, na memória vamos trabalhar sempre com os 64 bits, no mínimo.

Qualquer acesso diferente, será feito pela CPU na cache, como veremos mais adiante.

Vamos clarificar o porquê de toda esta conversa.

Se pretendemos que cada chip contribua simultaneamente com 1 Byte para o barramento de dados, temos que fazer o endereçamento na memória desprezando os 3 bits de menor peso, afetando essa redução só o endereço de colunas, para que se tenha o mesmo endereço repetido em todos os chips, como se pode constatar no gráfico representativo do conjunto de 8 chips na Figura 6c.

Endereçamento da memória enquanto ainda composta por 8 chips e 1024 bytes a endereçar.

Por exemplo, quando a CPU requisita um dado da posição de memória 00010 01 011, o CM vai selecionar na linha 00010, todas as colunas com o endereço 01, portanto os 8 bytes 01 000 a 01 111, através de sinais de controlo que envia à memória. Neste caso enviará

- um RAS de 00010 e

- um CAS de 01.

Continuando a pretender os 64 bits na saída, mantêm-se 2 bits para endereçamento de coluna. Temos 1024 bytes a endereçar, sendo divididos por 32 linhas e por 4 colunas (x8). Ver Figura 7.

Mas admitamos agora que a memória que se pretendia analisar tinha 4 KBytes de capacidade.

Devemos então juntar mais 24 chips ao lado dos já existentes, para obtermos o valor desejado?

Endereçamento da memória de 4KBytes constituída por 8 Dies de 4 Bancos. A CPU envia um endereço de 12 bits, tantos quantos os necessários para os 4096 bytes. O Controlador gera os códigos BA0 e BA1, que definem cada Banco, com base nos bits E11 e E10. Envia os bits E9 a E5 com o código RAS e E4 e E3 com o código RAS.

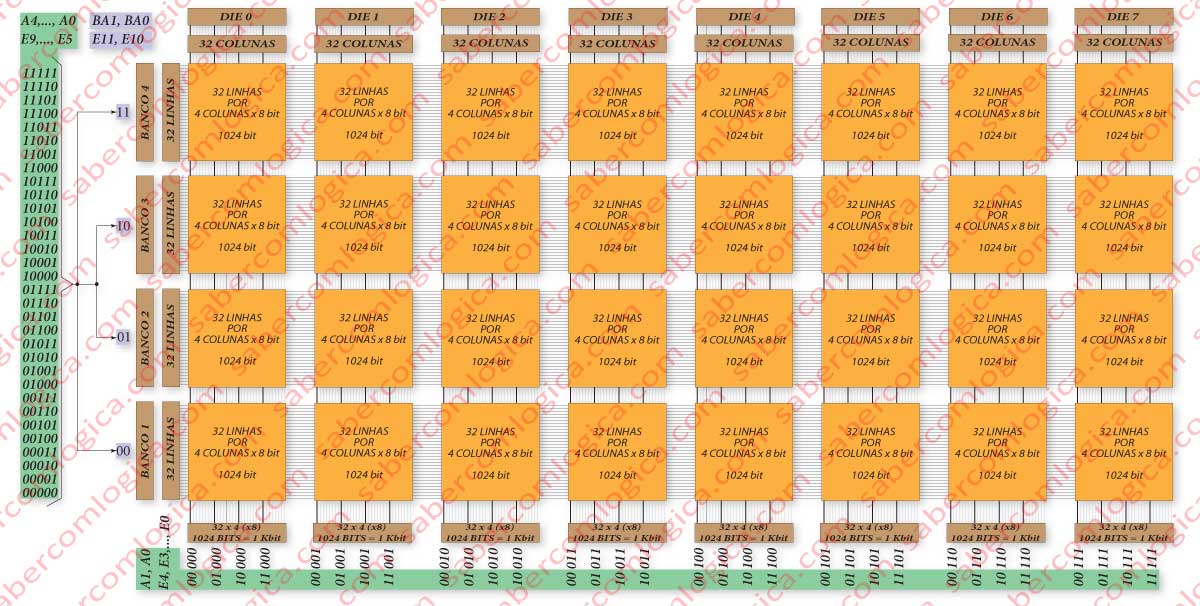

Certamente que não. Para esta nossa nova pretensão vamos criar um circuito integrado que engloba quatro chips iguais aos nossos num só circuito integrado a que vamos chamar Die, que também é um circuito integrado por definição. Cada Chip dentro deste Die constitui aquilo a que vamos chamar Banco, tendo nós assim Dies de 4 Bancos. E são 8 Dies destes que vamos juntar no circuito impresso a que chamamos DIMM, obtendo assim um módulo de memória com 4 KBytes, como o representado na Figura 9.

Mas porquê criar 4 Bancos dentro de um Die ?

Tal como nas colunas, vamos endereçar as linhas omitindo 2 bits (neste caso os de maior ordem), aos quais vão corresponder dois novos sinais enviados pelo controlador à memória, BA0 e BA1, que definirão em cada caso e em conjunto, qual o Banco que está a ser acedido, conforme a sua combinação 00(0), 01(1), 10(2) e 11(3). Ver Figura 8.

Representação de um módulo de memória de 4 KBytes dividido em 8 Dies por sua vez compostos por 4 Bancos, cada banco constituído por uma matriz quadrada de 32 linhas por 4 colunas de 8 bits cada, representando 1024 células de memória.

COMO OPERA UMA SDRAM

Vamos agora intercalar uma referência à forma de operar de uma memória SDRAM, para que seja mais fácil de entender a existência de hierarquias de memória e a própria forma de acesso para que a SDRAM foi concebida.

Uma memória SDRAM tem uma determinada latência no acesso. Por cada vez que acede a uma linha diferente, é executado um processo interno na memória, que iremos analisar mais adiante, que exige tempos de espera de cerca de 45 ns (nanossegundos) numa SDRAM de 133 MHz, entre o pedido de leitura e a leitura da resposta.

Nestas condições, é necessário tirar o máximo proveito do acesso que é feito a cada linha enquanto a mesma se mantém ativa. Com esse fim, as memórias SDRAM foram concebidas para acessos em rajada (burst), isto é, uma vez definido o endereço da coluna a ler, a memória ativa um contador que fará 1, 2, 4 ou 8 acessos seguidos que corresponderão a outras tantas palavras de 64 bits, ou ainda uma leitura de página, isto é, de todas as colunas de uma linha de um banco, nos 8 Dies. Desta forma cada acesso é efetuado num ciclo de clock da memória, que no caso de uma memória com uma frequência de clock de 133 MHz corresponderá a 7,5 ns por leitura, reduzindo assim substancialmente o tempo de acesso médio, embora a espera pelo início da resposta se mantenha em 45 ns.

Vamos fazer um ponto de situação da nossa evolução. Temos então um conjunto de 4.096 x 8 bits (4 KB), ou seja, 32.768 pequenas lâmpadas rotas (que vão perdendo carga e é preciso recarregar) e precisamos de aceder a cada uma individualmente, embora as localizemos em conjuntos de 8.

Já analisámos a forma de organização da memória. Já temos uma memória de 4 KBytes, correspondente a 1 módulo DIMM composto por 8 Dies, sendo cada um constituído por 4 Bancos de 32 linhas por 4 colunas x8.

Vamos agora analisar o interior de um Die de 4 Bancos, quais são os sinais que recebe e envia, o que significam e como os trabalha.

O INTERIOR DE UM DIE

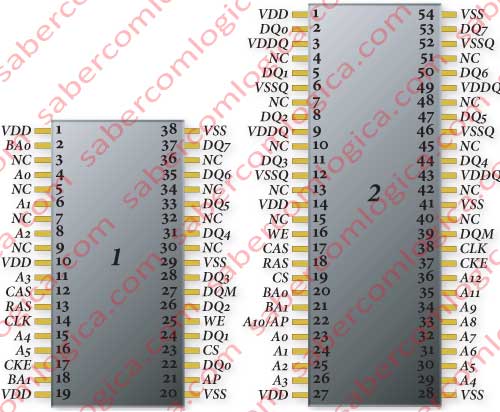

Para esse efeito elaborámos um gráfico em que colocámos esse conjunto dentro de um Die, na Figura 11. Reduzimos os pinos não essenciais e reposicionámos os outros pinos, por forma a obtermos uma forma viável de elaborar os circuitos de ligação sem criar uma enorme confusão de linhas.

Representação gráfica de um mesmo Die de duas formas diferentes. O nº 1 corresponde a uma adaptação imaginária do número de pinos e sua colocação por forma a permitir a representação de ligações do quadro com conteúdo que vamos ver na Figura 11. O nº 2 corresponde à representação real de um DIE de uma memória SDRAM de 256 MB que servia de base a este trabalho.

Para que isso melhor se possa entender juntamos uma representação do nosso Die e do Die de 256Mb do módulo de 256 MB que a partir daqui vai servir de base a este trabalho, na Figura 10.

Vamos começar por perceber o que significa cada um dos conjuntos de letras que se veem junto de cada pino.

VDD – Fornecimento de energia

VSS – Ligação à terra

VDDQ – Fornecimento de energia aos Buffers de entrada e saída (Pinos DQ), com características de imunidade ao ruído (interferências eletromagnéticas)

VSSQ – Ligação à terra dos Buffers de entrada e saída com as mesmas características

CLK – Sinal de Clock – Na SDRAM o S significa Synchronised, isto é, funciona sincronizada com o sinal de Clock da Placa Mãe, que lhe é enviado por este pino.

CKE – Clock Enable – É através deste sinal que se pode suspender o funcionamento da memória. Todos os registadores, que respondem ao flanco ascendente do sinal de clock, recebem estes dois sinais. Se CKE estiver em baixo (0) as básculas não funcionam, mantendo-se fixos os valores à entrada e saída do DIE.

WE – Write Enable – É através deste sinal que a memória executa uma operação de escrita ou leitura. É ativo em baixo (0), isto é, quando está em baixo indica escrita.

CAS – Colune Adress Strobe – É este sinal que indica à memória que os valores colocados nos pinos de endereço se destinam ao descodificador de colunas. São portanto desviados para o registador de endereços de coluna. CAS é ativo em baixa.

RAS – Row Adress Strobe – Este sinal indica à memória que o valor colocado nos pinos de endereço se destina ao descodificador de linhas, pelo que é colocado no registador de linhas. RAS é ativo em baixa.

CS – Chip Select – Este sinal desativa o funcionamento de um DIE, impedindo a entrada dos sinais de controlo. No entanto a operação que estiver em curso segue até ao fim. É ativo em baixa. É específico para um conjunto de DIEs predefinido.

BA0 e BA1 – São dois sinais que em conjunto permitem definir o Banco ativo. Como já vimos resultam dos dois bits de maior peso do endereço recebido pelo controlador da CPU.

DQM – DQ Mask – Este sinal, durante um ciclo de escrita, se colocado em alta, impede a entrada de qualquer valor pelos pinos DQ. Durante um ciclo de leitura impede a passagem pelo buffer de saída para os pinos DQ se colocado em alta. Nos pinos de entrada do DIMM existem 8 sinais DQM0 a DQM7, cada um destinado a um DIE.

A0 a A12 – Pinos onde são colocados os valores dos bits de endereço que se destinam a linhas ou colunas, conforme o sinal ativo seja RAS ou CAS.

A10/AP – Quando o valor aqui colocado pertencer a um endereço de linha é válido como tal, isto é, como endereço. Quando esse valor pertencer a um endereço de coluna, passa a ter o significado de AP.

DQ0 a DQ7 – É nestes pinos que são colocados os dados de saída ou entrada na memória, conforme se estiver num ciclo de leitura ou escrita.

NC – Not Conected – Não ligado internamente.

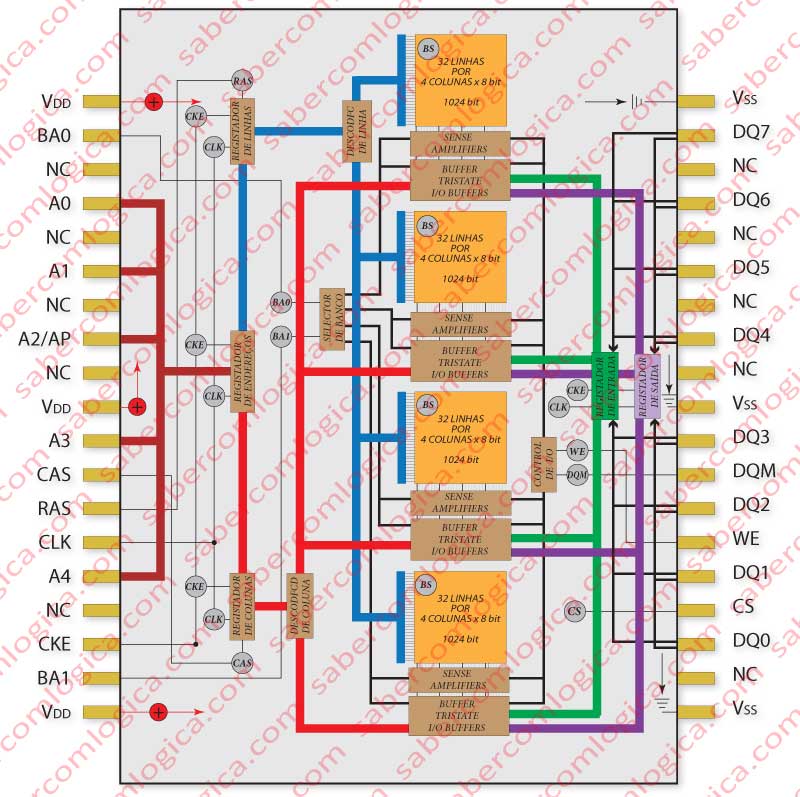

Representação gráfica de um DIE da nossa memória inserida dentro do encapsulamento de um DIE real. A posição e quantidade dos pinos foi propositadamente alterada por forma a que fosse possível representar todas as ligações e correspondências sem criar demasiada confusão de linhas. Os pinos essenciais à compreensão da realidade de um DIE de uma memória SDRAM foram mantidos.

COMO SE ACEDE A UMA POSIÇÃO DE MEMÓRIA

O nosso objetivo, para já, é acompanhar o percurso dos dados entre a MP e a CPU.

Portanto, vamos assumir que estamos em comandos de leitura ou escrita e que o modo de rajada definido é 1, isto é, a memória só lê ou escreve uma palavra de cada vez.

Vamos então analisar como é que a memória chega ao valor pretendido na posição de memória indicada pelo endereço na memória imaginária de 4KB que está a servir de base ao nosso trabalho.

Do controlador de memória chegam os sinais já falados, BA0, BA1, CAS, RAS, WE, DQM, CS, CLK, CKE.

CLK e CKE estão ambos em alta pois estamos numa operação simples de leitura ou escrita.

CS está em baixo pois o DIE está selecionado. Aliás todos os DIE estão selecionados, para podermos ter os 8 Bytes no barramento.

DQM da mesma forma tem que estar em baixa, para permitir tanto a leitura como a escrita, neste DIE e em todos os outros.

Quando os bits de endereço são colocados no registador de endereços (Figura 12 nº 5) também os sinais RAS, CAS e WE são colocados no registador de sinais (Figura 12 nº 6).

Os sinais RAS, CAS e WE vão ser os bits de controlo de um MUX de que sairão os sinais principais de comando da memória (Figura 12 nº 1).

Para já fica só a indicação de que será o sinal saído deste MUX, que ativará o sinal de clock das básculas do registador de linha (Figura 12 nº 2), registador de coluna (Figura 12 nº 3) e do registador do modo de registo (Figura 12 nº 4), conforme seja o caso.

Os pinos A0 a A4, onde se encontra o valor do endereço fornecido pelo CM (Controlador de Memória), está ligado à entrada de todos estes registadores esperando pelo sinal que o faça passar à saída.

O comando de uma memória SDRAM é bastante complexo, pelo que não vamos para já importar-nos com a forma como os sinais são obtidos nem com o significado de alguns componentes que vão aparecendo. Vamos simplesmente registar a sua existência. Já iremos analisar o comando de seguida.

Para já só nos interessa analisar a forma de acesso às células da matriz, pelo que nos vamos preocupar só com os registadores de linha e coluna e com a sua ativação ou não ativação, que como já dissemos é feita por um sinal de clock que está ligado a cada um.

Quando o endereço fornecido pelo CM diz respeito a uma linha, será o registador de linha a ser acionado, passando o endereço nas suas entradas para a saída e consequentemente para o desmultiplicador (DEMUX) assinalado na Figura 12 nº 11.

Um DEMUX de 5 para 32, o número de bits de endereço (5) e o número de linhas (32). Mas não vamos por esse caminho. Certamente que numa memória com a dimensão da nossa, essa seria a solução. Mas estamos a analisar esta como forma de entender as reais.

Então vamos colocar 4 DEMUX de 3 para 8, sendo os 3 bits de seleção, os de menor ordem do endereço. Na entrada de cada um destes DEMUX, estará a linha que vem de um DEMUX de 2 para 4 em que os bits de seleção são os 2 de maior peso do endereço. No nosso caso está selecionada a linha correspondente ao endereço 00000.

Qual a vantagem de proceder desta forma?

Bom, no nosso caso não é significativa, mas em vez de 32 portas AND com 6 transístores temos 32 portas AND com 4 transístores e 4 com 3 transístores. Em lugar de 192 transístores teremos 140. Uma redução de 22%. Que podia ser melhor ainda com um algoritmo bem estudado e pensado.

Agora passemos de 32 para 8.192 linhas, como numa SDRAM de 256 Mbit e tiremos conclusões. Um bem elaborado e complexo algoritmo de desmultiplexação fará certamente maravilhas em comparação com a solução imediata e imaginária de um DEMUX de 12 para 8.192.

Mas continuemos com a nossa solução simples para uma míni memória.

A linha encontrada pelo DEMUX é ativada em todos os Bancos do DIE, pois o descodificador de linhas está ligado a todos os Bancos. São agora os sinais BA0 e BA1 que vão designar em que Banco está a posição de memória que me interessa.

A seleção do Banco é feita pelos sinais BA0 e BA1 num seletor de banco, indicado na Figura 12 nº 7, onde são combinados com outros, fazendo parte da estrutura do comando da memória que por agora não interessa. Para já vamos determinar que temos selecionado o Banco 0, sendo portanto B0=0 e B1=0.

Fica assim selecionada uma linha e um Banco.

Chegou agora a vez de o CM enviar o endereço de coluna e ativar o registador de endereços de coluna, sendo o valor do mesmo colocado na sua saída e consequentemente no DEMUX de colunas (Figura 12 nº 8).

No nosso caso é um simples DEMUX de 2 para 4 em que os bits de seleção são os bits de maior ordem do endereço. Repare-se que as portas de seleção deste DEMUX são portas NAND, o que significa que a saída selecionada pelos bits de seleção será a única que está em baixa, contrariamente aos DEMUX com portas AND, em que a saída selecionada era a única que estava em alta (a mesma situação se passa com o seletor de Banco).

Basicamente passa-se com este DEMUX o mesmo que com o descodificador de linhas, só que sempre em menor escala (com menos 3 bits de endereço), mas o resultado é sempre o mesmo. Uma coluna fica selecionada em cada banco. Mas de uma forma completamente diferente.

Enquanto nas linhas o DEMUX se limita a ativar (colocar em baixa) uma linha em cada Banco, nas colunas o que se passa é completamente diferente. Vejamos então.

À saída de cada linha de bit de cada Banco encontra-se um Sense Amplifier (Figura 12 nº 9)e duas portas Tristate I/O (Figura 12 nº 10), uma para a entrada (I) e outra para a saída (O) do valor do bit a escrever ou ler.

Tanto a linha de entrada como a linha de saída de cada bit passam por uma porta Tristate ativa em baixa (a zero). Diz-se quando a porta Tristate está em alta, que se encontra em alta impedância (HiZ). Isto significa que oferece alta resistência à passagem de qualquer valor, isto é, não deixa passar nada, o interruptor está desligado.

Sobre o Sense Amplifier e o Buffer Tristate, será devidamente desenvolvida a análise à sua função e sua forma de funcionamento, já de seguida.

Normalmente estas portas colocam-se quando existe a possibilidade de colocar vários valores numa mesma linha, como é o caso representado na Figura 12, em que os valores das quatro linhas 15 concorrem todos na mesma linha 16. Nestes casos é preciso garantir que, de cada vez, só um dos valores passa para a referida linha, sob pena de poder causar graves avarias, resultantes de curto-circuitos provocados pelo conflito entre diferentes valores que se tentam impor na mesma linha.

Como é evidente a linha 15 representa as 8 linhas de bit do byte e a linha 16 também representa as 8 linhas dos bits do byte que transporta de cada vez.

É por esta razão que no seletor de colunas, só uma saída, a selecionada, está em baixa, ativando assim as correspondentes portas Tristate de entrada ou saída, consoante se trate de uma escrita ou uma leitura.

O sinal WE (Write Enable), que define o modo de escrita (0) ou leitura (1), liga em conjunto com o sinal de seleção de coluna a uma porta OR que fica antes da Porta Tristate de entrada dessa linha de bit.

A negação de WE liga também, junto com o seletor de coluna a outra porta OR que fica antes da porta Tristate de saída dessa linha de bit. A estas portas OR liga também o sinal DQM que, quando em alta, impede tanto a entrada como a saída.

E como toda esta seleção é comum aos Buffers existentes à entrada de cada Banco, também a linha do seletor de Banco (mais uma que está em baixa quando é selecionada – estão a perceber o porquê da diferença?) vai ligar a cada uma destas portas OR.

Ora, como sabemos, uma porta OR só dá saída em baixa (falso) quando todas as entradas estão em baixa (são falsas). Portanto, para uma porta Tristate se ativar (0) é necessário que se cumpram 4 condições:

- Pertencer à coluna selecionada

- Estarmos num ciclo de escrita ou de leitura, alternando duas portas conforme a situação

- Que DQM não esteja ativo.

- Que a porta pertença ao Banco ativo

Agora vamos estender o que dissemos relativamente a uma porta, às 7 que se lhe seguem e compõem o Byte. Estas podem estar todas ativas em simultâneo pois vão descarregar em linhas diferentes, uma vez que a cada bit da mesma ordem de cada Byte corresponde uma linha que caminha até ao registador de saída (Figura 12 nº 14). Da mesma forma há uma linha para cada bit da mesma ordem de cada Byte que caminha do registador de entrada (Figura 12 nº 13) para a linha de bit.

É assim, desta forma, que se cruzam as BL (Bit Line ou linhas de bit ou colunas da matriz), com a linha ativa da matriz, selecionando assim as células a ler ou escrever e transportando o seu valor para o registador de saída ou a partir do registador de entrada. Como é que isto é feito, vamos já de seguida analisar em pormenor.

A CÉLULA DE MEMÓRIA SDRAM

Em eletrotecnia, um interruptor está fechado quando deixa passar corrente elétrica e está aberto quando aquilo que une os dois polos está aberto e portanto a corrente não passa. Vamos tratar os transístores como interruptores que são, portanto quando dissermos que está fechado a corrente elétrica passa e quando dissermos que está aberto não passa.

Esta observação é feita porque é com a situação oposta que mais frequentemente nos deparamos. Nós passamos quando as coisas estão abertas e não passamos quando estão fechadas.

SENSE AMPLIFIER

Um Sense Amp (Sense Amplifier) é um dispositivo com capacidade de escutar ou sentir o conteúdo das células de memória e amplificá-lo.

A carga armazenada num condensador com a dimensão de alguns nanómetros é de valor muito baixo, isto é, a sua capacitância é muito pequena. Temos aqui um novo conceito, o de Capacitância.

Capacitância, em eletrónica, é a capacidade de qualquer corpo reter carga elétrica, desde que isolado.

E porquê este conceito agora?

Porque a carga retida pelo condensador, isto é, a sua capacitância será afetada pela capacitância da BL (Bit Line) e vice-versa. O que não é difícil de entender, sabendo que a mesma BL serve milhares de células e sabendo da nano dimensão do condensador.

Como facilmente se conclui do que vimos dizendo, se a carga do condensador for descarregada numa BL com carga indefinida, tenderá a dissipar-se na mesma e a não garantir a possibilidade de leitura e identificação do valor nele contido.

Por todas estas razões são utilizados os Sense Amplifiers, que se encarregam, devidamente instruídos pelo CM (Controlador de Memória), da leitura do valor contido no condensador.

Sempre que a linha de endereço é ativada, todas as células dessa linha são ligadas às respetivas BL, mesmo que o valor não pertença à coluna desejada. Entenda-se que, à ativação da linha, corresponde a abertura do transístor que liga o condensador da célula à respetiva BL. As operações de leitura ou escrita são destrutivas, isto é, caso não consiga ser restaurado o valor contido em todas as células (bits) de uma linha ativada, o seu conteúdo vai perder-se, pois a tensão acumulada ou não no condensador vai dissipar-se na BL

Portanto, não é só na BL em que está o valor a consultar que se vai passar o atrás descrito, mas em todas as BL (Bit Line) que intersetem a linha ativada.

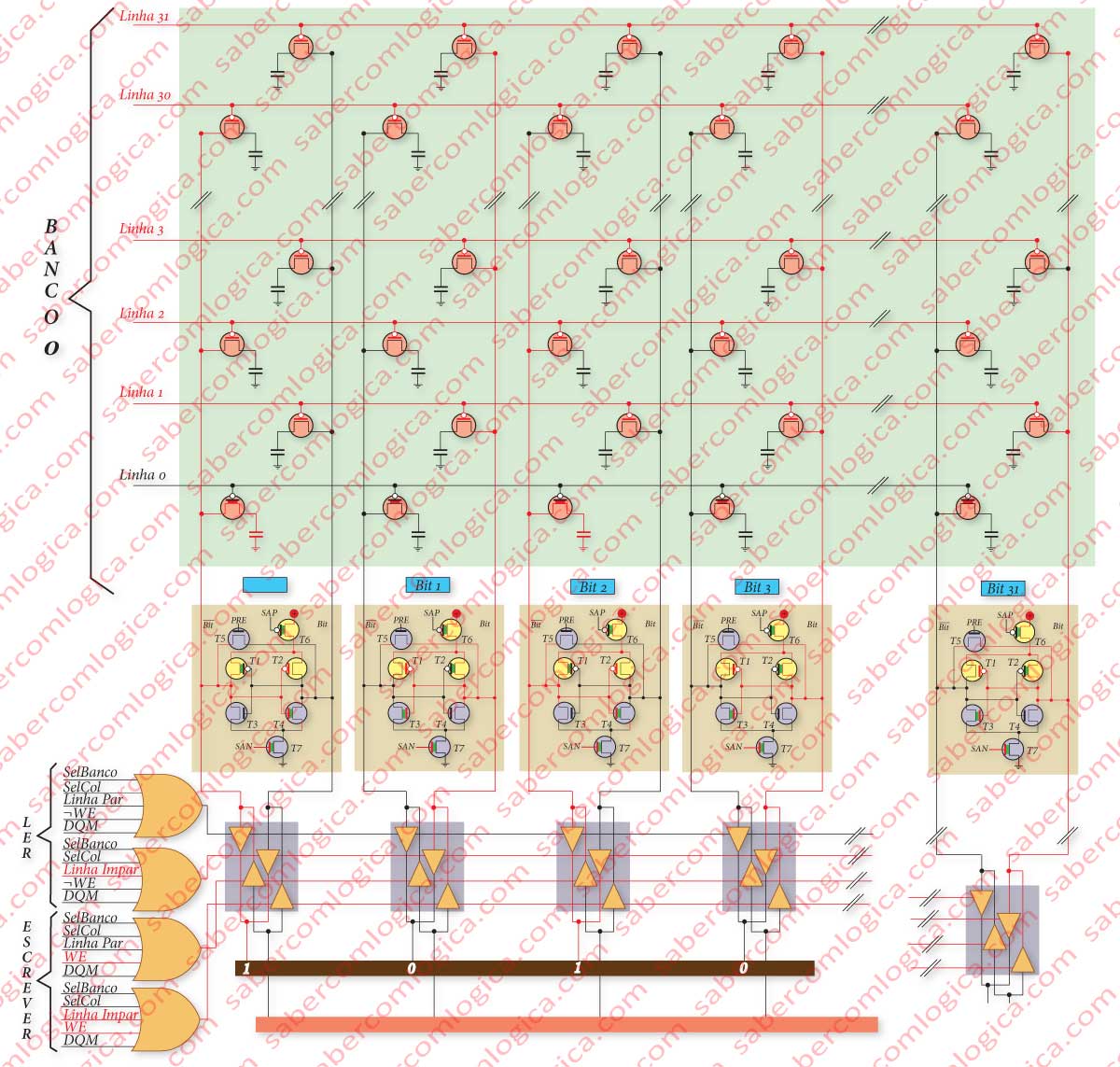

Para bem entendermos a forma de funcionamento do SA (Sense Amplifier), vamos ter que acompanhar com a descrição pormenorizada, a forma de acesso a uma célula de memória para leitura e escrita, Figura 15.

As linhas que vão às portas OR responsáveis pela seleção de colunas, estão assinaladas com a designação das entradas e preto ou vermelho conforme lhes corresponda um estado lógico 0 ou 1.

Este quadro é apresentado a partir deste ponto, porque corresponde a uma pormenorização do quadro anterior, que não detalha como é feito o acesso à matriz da memória, mas simplesmente como é selecionada uma linha, uma coluna e uma operação.

Repare-se que as células de cada linha se inserem intercaladamente em duas BL paralelas.

Concretamente as células da linha 0 inserem-se numa BL à sua esquerda e as da linha 1 numa BL à sua direita. Generalizando, as linhas de endereços pares estão inseridas numa BL (a da esquerda) e as ímpares na outra BL (a da direita).

Repare-se ainda que ambas estas BL vão ser tratadas pelo mesmo SA, isto é, existirá um SA por cada duas BL. Mas as duas BL estão a desempenhar o papel de uma, porque servem ambas a mesma coluna de células.

Desta forma o SA pode utilizar as duas BL, sendo que para cada linha de endereço ativa só uma das BL ligada às células dessa linha. A outra BL está isolada das células que serve.

Célula de memória no silício. BL (Bit Line) e condensador são positivos, pelo que o transístor da linha de endereço é um PNP, activo a 0.

E para que serve esta duplicação?

O SA utiliza duas linhas de bit para executar a sua função. Uma das BL deve estar completamente isolada de qualquer influência que não a do SA. Para suprirmos esta exigência, utilizámos esta estratégia.

Como se pode verificar, cada célula da memória DRAM é composta por um transístor e um condensador que funcionam de acordo com o esquema junto e devidamente descrito na legenda de apoio da Figura 13.

A BL transporta o valor lido ou a escrever na célula selecionada através do SA (Sense Amplifier). É a ativação das portas tristate que define qual a coluna selecionada para ser lida ou escrita. Os quadros da Figura 14 ilustram as várias fases do funcionamento de um SA.

Vamos introduzir aqui mais um conceito fundamental no funcionamento de uma memória dinâmica. O de precarga.

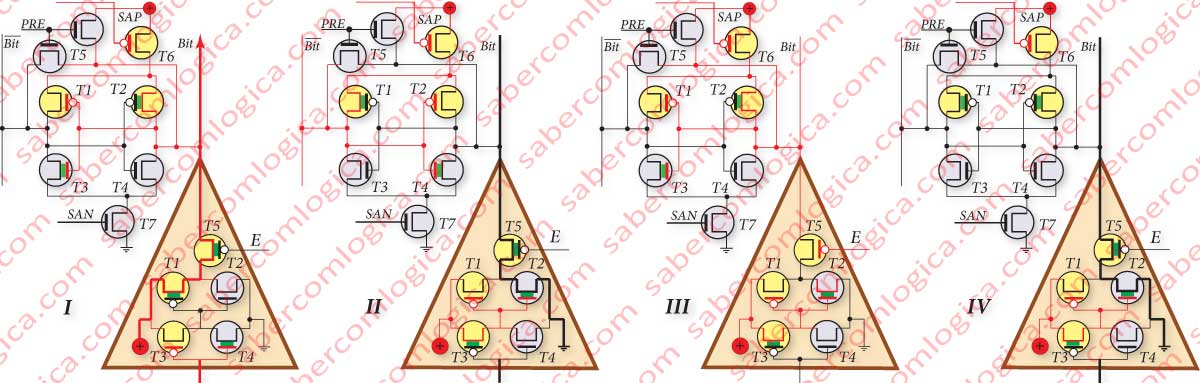

Quadros de análise do comportamento de um Sense Amplifier nas diversas situações do seu funcionamento.

PRECARGA

Antes de mais queremos deixar a indicação de que, nos transístores CMOS, o estado lógico 0 é representado por tensões entre os 0 e VDD/2 e o estado lógico 1 por tensões entre VDD/2 e VDD, sendo que VDD é a tensão de alimentação do circuito.

A Precarga consiste no carregamento de todas as BL do Banco selecionado ou de todos os Bancos, conforme a opção escolhida, até um razoável valor da sua capacitância, superior a VDD/2 e na curto-circuitagem das mesmas por forma a atingir o seu total equilíbrio.

É através do SA que o controlador de memória executa o comando de Precarga. Quando esta operação é efetuada, todas as linhas de endereço são desativadas, estando portanto todas as BL isoladas. Esta é a situação demonstrada no Quadro I. Repare-se que o sinal de Precarga abre o transístor T6, ficando a alimentação cortada ao circuito. Entretanto fecha os dois transístores T5 que alimentam e curto-circuitam as duas BL, que assim ficam equilibradas.

Uma vez efetuada a Precarga, a memória está preparada para as operações de leitura ou escrita. A precarga é a última operação efetuada após a conclusão do comando ACTV, deixando a SDRAM preparada para novo comando ACTV.

O SENSE AMP E O RESTAURO

Partindo da situação do Quadro I, fechado o transístor T5 pois a Precarga foi concluída, procede-se à ativação da linha do banco e do SA. Ao ativarmos a linha, o condensador fica em comunicação direta com as respetivas BL, transferindo para elas a sua capacitância ou retirando-lhes um pouco da mesma, conforme esteja no estado lógico 1 ou 0. Vamos supor que está no estado lógico 1, portanto carregado.

Como as BL estão em carga, a BL que liga a esse condensador não recebe dele qualquer valor. Só começa a receber carga do condensador conforme ambas forem descarregando para terra, através do SA e dos transístores T3 e T4, a carga que tinham.

Esta é a situação mostrada no Quadro II, em que os transístores T1 e T2, alimentados pelas BL, continuam a cortar a alimentação às BL e em que os transístores T3 e T4 ligam as BL à terra.

As BL estão a descarregar e são elas que alimentam os Transístores CMOS T1/T3 e T2/T4.

Agora vai entrar em ação a tal BL que não está ligada a nenhum condensador, porque os que lhe pertencem estão em linhas inativas. Vai existir uma diferença entre esta e a que está ligada ao condensador da linha ativa. Estão as duas igualmente carregadas e a descarregar em simultâneo. Mas uma está a receber a carga do condensador a que está ligada e a outra não.

Logo, haverá um instante em que uma das BL passa ao valor correspondente ao estado lógico 0 e a outra BL ainda se mantém no estado lógico 1.

É nesse momento que a ação da BL que passou a 0 sobre o transístor CMOS T2/T4, vai fazer uma espécie de SET ao circuito. Acompanhe-se pelo Quadro III. O transístor T2 abriu e passou a fornecer alimentação à BL que ainda está no estado lógico 1, reforçando assim esse estado lógico. Como o transístor T4 fecha, a descarga desta linha é parada.

Assim, o condensador é recarregado em pleno com o valor lógico que possuía e a informação é fornecida para o exterior com o valor lógico 1 totalmente restaurado e à tensão máxima do circuito.

Por outro lado, a ação da saída deste CMOS sobre o CMOS T1/T3 com que está cruzado, fechando T1 e abrindo T3 vai reforçar o estado em que ele se encontra, mantendo a interrupção de alimentação à BL e a continuação da sua ligação a terra, esgotando-a por completo até ao mais puro estado lógico 0.

Suponhamos agora que o condensador em questão se encontrava no estado lógico 0, isto é, descarregado. Neste caso é a BL que lhe está ligada que descarrega mais depressa, pois além de estar ligada à terra também dissipa carga para o condensador, sendo portanto a primeira a atingir o nível correspondente ao estado lógico 0.

Para não alongar muito a descrição diremos que provoca uma reação totalmente contrária à anterior, forçando o estado lógico 1 na BL sem ligações e provocando um RESET ao conjunto, criando o estado lógico 0 perfeito na BL que liga à célula que está a ser acedida e consequentemente, no condensador que lhe está afeto e na saída para o exterior, como se pode verificar pela apreciação do Quadro IV.

Esta situação passa-se em todas as BL do Banco em leitura, mesmo as que não pertencem às colunas selecionadas, pois ao ativar a linha de endereço abrimos todos os transístores que ligam os condensadores às BL nessa mesma linha, precisando portanto esse valor de ser restaurado no condensador.

Portanto, a ação do SA não se limita a ampliar o sinal para o exterior mas também e principalmente ao seu restauro em todas as células afetas à mesma linha de endereço. Espero que tenha sido bem entendido o conceito de Precarga e a sua necessidade, bem como a forma de atuar do SA (Sense Amp).

LEITURAS E ESCRITAS

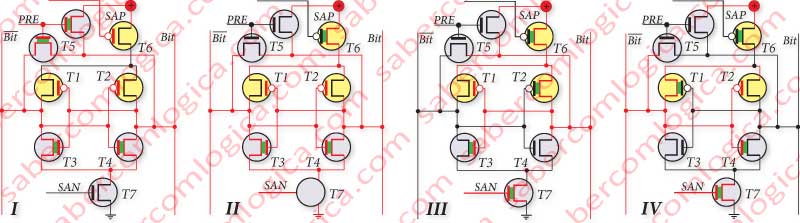

BUFFER TRISTATE

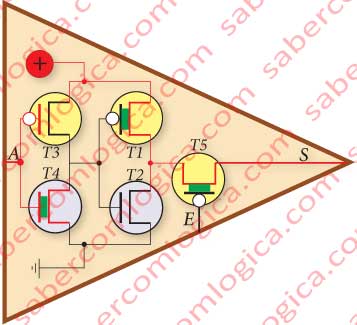

Buffer Tristate. A – Entrada; S – Saída; E – Enable;

Para analisarmos o Buffer Tristate (BT), comecemos por olhar para a Figura 16. O corte da comunicação com o exterior é feito pelo interruptor correspondente ao transístor T5, que está ligado a uma linha que ativa ou desativa a porta. Entrada E (Enable), que se E=0 ativa a porta e se E=1 corta qualquer comunicação com o exterior da memória, colocando o BT em alta impedância (Hz).

Entre a entrada do BT e o interruptor T5 temos dois transístores CMOS ,um a seguir ao outro, o que é equivalente a duas portas NOT seguidas, reproduzindo à saída da segunda precisamente o que se passava na entrada da primeira. Aparentemente irrelevantes.

Mas com uma pequena grande diferença. A ligação dos transístores T2 e T4 à terra e dos transístores T1 e T3 à alimentação.

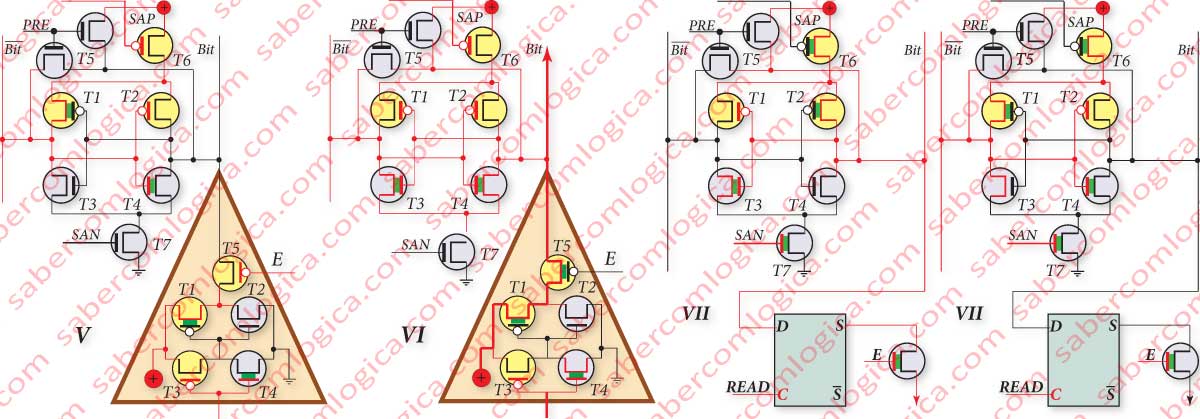

Vamos ver agora de seguida, na análise das diferentes hipóteses de escrita, o comportamento do BT.

LATÊNCIAS

Para a análise que vamos fazer é importante ter uma noção dos tempos de espera entre os diversos comandos.

Entre o comando PRCG e o comando ACTV haverá uma espera de um determinado número de nanossegundos, que será traduzido em ciclos de clock conforme a frequência da memória, com o fim de permitir a estabilização dos valores nas BL. Este tempo de espera chama-se tRP.

Entre o comando ACTV e os comandos READ ou WRITE também haverá um determinado tempo de espera em nanossegundos, convertido em ciclos de clock de acordo com a frequência da memória, para permitir que o SA faça o seu trabalho de sentir e ler, podendo depois transmitir essa informação. A este tempo de espera chama-se tRCD.

Entre o comando ACTV e PRCG haverá um determinado tempo mínimo a ser cumprido, em nanossegundos convertidos em ciclos de clock, para que os SA possam completar o seu trabalho fazendo o restauro dos valores das células lidas. A este tempo de espera chama-se tRAS.

Este último tempo (tRAS) é o tempo mínimo que a linha tem que estar ativa e em que os SA também têm que estar ativos, ou alimentados.

ESCRITA

Na situação de escrita, os SA das colunas selecionadas têm que ser desligados, pois a sua reação às variações provocadas pela escrita nas BL, iria gerar efeitos contrários aos pretendidos.

Vamos seguir pela Figura 17.

Análise do comportamento do buffer tristate. Quadros I, II, III e IV.

1. O valor a escrever é 1 e o valor memorizado é 1.

A entrada a 1 faz com que a ação conjunta dos 2 transístores CMOS abra o transístor T1, deixando passar a alimentação do BT para a BL, limitando-se a manter a situação estável, como se pode ver no Quadro I

2. O valor a escrever é 0 e o valor memorizado é 0.

A entrada a 0 faz com que a ação conjunta dos 2 transístores CMOS abra o transístor T2, ligando a BL à terra, limitando-se a manter a situação estável, como se pode ver no Quadro II

3. O valor a escrever é 0 e o valor memorizado é 1.

Como impor um valor 0 sobre uma linha carregada a 1?

Só por escoamento do valor da linha carregada. E é isso que o BT provoca. A entrada a 0 faz com que a ação conjunta dos 2 transístores CMOS abra o transístor T2 deixando a BL ligada a terra, para onde se escoam todos os eletrões existentes na BL e no condensador da célula de memória, que assim ficará num estado lógico 0, como se pode ver nos Quadros III e IV, que ilustram a situação antes e depois da ativação do BT..

Agora imaginem que o SA estava ligado, a forçar o estado lógico 1 e a restaurar o valor da célula. A alimentação do SA escoava-se para a terra do BT e tínhamos um curto-circuito que podia destruir um circuito integrado ou criar alguma situação inesperada no valor da célula. Com o SA desligado não corremos riscos de ações inesperadas e física ou logicamente destrutivas.

Análise do comportamento do buffer tristate na escrita nos quadros V e VI. Análise do tratamento dos dados lidos das células nos quadros VII e VIII.

4. O valor a escrever é 1 e o valor memorizado é 0.

Quando a entrada do BT está a 1, o transístor T1 está aberto e a alimentação do BT invade a BL, todo o SA e o condensador, que ficará carregado no absoluto estado lógico 1, como se pode ver nos Quadros V e VI, que ilustram a situação antes e depois da abertura do BT.

Se o SA estivesse ligado, a forçar o estado lógico 0 e a restaurar o valor da célula, a alimentação do BT escoava-se para a terra do SA e repetia-se a situação. Diremos o mesmo: com o SA desligado não corremos riscos de que tal situação aconteça.

LEITURA

O comando READ vai atuar como sinal de clock nos trincos onde estão ligadas as BL. O valor já sentido e lido pelos SA das células da linha ativa será então memorizado nos trincos. O Quadro VII representa esta situação para a leitura do valor 1 e o Quadro VIII representa esta situação para a leitura do valor 0.

Quando do fim da última leitura será emitido o comando PRCG, desde que se encontre já esgotado o tempo de espera entre ACTV e PRCG (tRAS). Se assim não for essa emissão terá que aguardar e deixar que tRAS se esgote.

Emitido o comando PRCG, vai o mesmo fechar a linha ativa e desligar o SA da sua alimentação convencional. Entretanto liga os transístores PRE, colocando o valor 1 nas portas dos transístores T5, criando assim a forma de alimentação própria da precarga.

Já analisámos os caminhos que os nossos estafetas têm de percorrer e os interruptores que têm que ligar e desligar para encher e esvaziar condensadores. Vamos então agora perceber quem e como os comanda.