Circuitos de memorização

O Flip-Flop SR, o Trinco D e a Báscula D são circuitos de memorização que permitem reter os valores dos bits de diferentes formas e que vamos analizar neste artigo.

Flip-flop SR ou Trinco SR

O flip-flop SR ou trinco SR é um circuito lógico capaz de servir como uma memória de um bit.

Vamos servir-nos de uma comparação com a abertura e fecho de uma porta (porta de casa, não porta lógica) que tem uma fechadura com trinco e uma maçaneta.

Para fechar a porta basta empurrá-la, assim ativando o trinco da fechadura. E permanece fechada por mais que se empurre, mesmo depois de deixar de a empurrar. A porta está no estado de fechada e assim vai ficar até que atuemos de outra forma e noutro local, concretamente puxando pela maçaneta, assim desativando o trinco da fechadura e abrindo a porta.

Uma vez aberta a porta de casa, podemos puxar pela maçaneta quantas vezes quisermos, mas a porta permanece aberta. A porta de casa transitou de estado e está no estado de aberta. Para a fechar teremos que a empurrar.

Vemos aqui duas ações sobre a porta: empurrar e puxar pela maçaneta. A primeira fecha a porta de casa quando está aberta e a segunda abre a porta de casa quando está fechada. A porta de casa só muda de estado quando a ação que a faz mudar de estado é executada. Repare-se que a não execução de nenhuma das ações mantém a porta no mesmo estado. E também que a execução simultânea das duas ações a coloca num estado indeterminado (depende da força que cada um fizer).

Bom, vamos deixar a nossa porta em paz e aberta, para que possamos ver para o exterior e vamos começar a analisar o circuito, que podemos ver nas Figuras 1 e 2.

O Flip Flop SR pode ser construído tanto com duas portas NAND como com 2 portas NOR.

A saída de cada porta é entrada na outra. E isto vale para as duas. É um circuito sequencial. As portas comunicam uma à outra o seu estado, assim influenciando mutuamente esse mesmo estado.

Às entradas sobrantes das duas portas vão estar ligadas as entradas A e B do Flip Flop SR.

Quando falamos na saída S de um Flip Flop SR, referimo-nos sempre à saída da sua porta superior. Na outra porta teremos sempre o valor negado dessa saída (¬S).

As funções do circuito correspondentes à execução das ações de empurrar e puxar pela maçaneta, são as de SET e RESET e dão origem ao seu nome SR.

A variável A assume o papel de SET, isto é, quando assume o valor 1 (empurrar) coloca a saída a 1 (fecha a porta).A variável B assume o papel de RESET, isto é, quando assume o valor 1(puxa a maçaneta) coloca a saída a 0 (abre a porta).

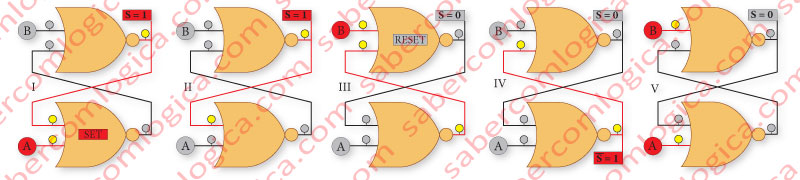

Para entendermos a forma de operar de um Flip Flop SR, vamos acompanhar a sua evolução para as diferentes variações dos valores das suas entradas, para os casos em que é constituído com portas NOR e com portas NAND que se juntam nas Figuras 1 e 2 respetivamente.

As combinações possíveis das entradas de um Flip Flop SR de portas NOR são (Figura 1):

- A=1 e B=0, como no Quadro I, em que é feito um SET ao circuito.

- A=0 e B=1, como no Quadro III, em que é feito um RESET ao circuito.

- A=0 e B=0, como nos Quadros II e IV, onde se pode verificar que essa combinação não altera o estado do circuito quer aconteça a seguir a um SET quer a seguir a um RESET.

- A=1 e B=1, como no Quadro V é uma combinação híbrida que deve ser evitada. Coloca as duas saídas sempre a 0. Não forçando uma das saídas a ser a negação da outra, tem um comportamento imprevisível.

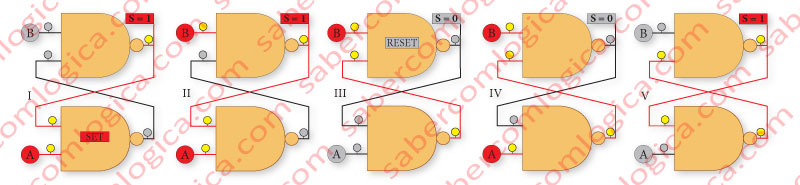

As combinações possíveis num Flip Flop SR de portas NAND são (Figura 2):

- A=1 e B=0, como no Quadro I, em que é feito um SET ao circuito.

- A=0 e B=1, como no Quadro III, em que é feito um RESET ao circuito.

- A=1 e B=1, como nos Quadros II e IV, onde se pode verificar que essa combinação não altera o estado do circuito quer aconteça a seguir a um SET quer a seguir a um RESET.

- A=0 e B=0, como na Quadro V é uma combinação híbrida que deve ser evitada, pois devolve sempre o resultado 1 em ambas as saídas das portas NAND. Não forçando uma das saídas a ser a negação da outra, tem um comportamento imprevisível.

Os comportamentos dos Flip Flop SR com portas NAND ou NOR são idênticos nas situações de SET e RESET.

Só diferem na situação em que A e B são iguais. A escolha do Flip Flop SR a utilizar deverá incidir naquele cuja situação de igualdade que possa acontecer não afete o estado do circuito.

Outra verificação que podemos fazer nos quadros evolutivos é que somente quando passa a 1 a variável que pode alterar o estado do circuito é que o mesmo muda. Após um SET a mudança de A não o altera. Somente a mudança de B para 1. Após um RESET a mudança de B não o altera. Somente a mudança de A para 1.

Este circuito permite converter pulsos de tensão (o clock p.e.) em estados contínuos de tensão, só alteráveis pela existência de outro pulso de tensão na outra entrada.

Até parece o interruptor lá de casa.

Carregando com o dedo num dos lados (um pulso numa porta) liga-se a luz que se mantém acesa até que carregando com o dedo do outro lado (com um pulso na outra porta) a luz se desliga.

Vamos poupar-nos a uma descrição exaustiva e cansativa de como com as ligações estabelecidas se consegue este comportamento neste circuito.

Os esquemas gráficos que estão junto permitem a análise dos mesmos e os conhecimentos já adquiridos sobre o comportamento de portas lógicas já vos permite chegar a conclusões.

Flip-flop ou Trinco D

O Flip Flop SR permite memorizar 0 ou 1 na saída, mas para isso precisa de duas variáveis que fornecem os dois sinais separados e que lhe permitem mudar de estado.

O Trinco D, que se apoia no Flip Flop SR (FFSR), permite memorizar na sua saída S o valor de uma variável D na sua entrada, por influência do clock C.

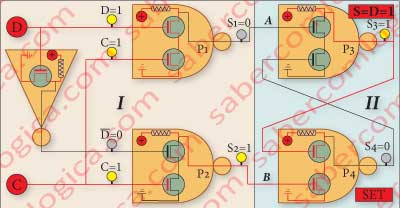

Na Figura 3, dividimos o Trinco em duas partes. A parte II corresponde a um FFSR e a parte I a um circuito prévio cuja função é colocar no lugar das entradas A e B do FFSR os valores que o farão responder em conformidade com o desejado.

Para isso as saídas das portas P1 e P2 do circuito prévio, são ligadas às entradas A e B do FFSR.

E então o que é que desejamos?

Ter o valor de D da entrada do Trinco memorizado na sua saída S por ação do clock C.

- Quando C e D têm o valor 1, a porta P1 retorna 0 (B=0) e a porta P2 retorna 1 (A=1). Nestas condições faz-se o SET do FFSR e o valor 1, o de D, é colocado na saída S do Trinco.

- Quando C tem o valor 1 e D o valor 0, a porta P1 retorna 1 (B=1) e a porta P2 retorna 0 (A=0). Nestas condições faz-se o RESET do FFSR e o valor 0, o de D, é colocado na saída S do Trinco.

Portanto o circuito prévio em conjunto com o FFSR, fazem o Trinco reagir como pretendido para a ação do Clock C.

Na Figura 4, podemos verificar o comportamento do Trinco D para as diversas variações de D e de C.

Nos Quadros 1 e 3 verificamos que com o C em 0 o circuito prévio devolve A e B a 1 para qualquer estado de D. As duas entradas a 1 num FFSR NAND mantém o seu estado. Portanto, com o clock em baixa (C=0) o Trinco D não reage a quaisquer modificações de D.

Nas transições dos Quadros 1→2 e 3→4, verificamos que quando C é 1 a porta onde D ou ¬D for 0 devolve 1, assim fazendo o SET do FFSR para D=1 e o seu RESET para D=0. Portanto quando C passa de 0→1 o valor D da entrada do Trinco passa para a sua saída S.

Nas transições dos Quadros 2→5 e 4→6, verificamos que qualquer alteração do valor de D altera o valor nas portas P1 e P2, consequentemente transformando uma situação de SET em RESET e vice-versa, assim alterando o valor da saída do Trinco para o novo valor de D. Portanto, quando C está em alta (C=1) o Trinco D coloca na saída S qualquer alteração da entrada D.

Báscula D

A Báscula D, tal como o trinco D, permite memorizar na sua saída S um valor D da sua entrada, por influência do clock C, só que, suprindo uma deficiência daquele. Precisamente a que está descrita na última verificação.

Enquanto o Trinco D é transparente, isto é, permite que o valor na sua saída mude de acordo com a variável de entrada dentro do mesmo ciclo de clock enquanto o clock está em alta, nas Básculas a variação da variável de entrada enquanto o clock está em alta não é refletida na saída. As Básculas não são transparentes. O valor da variável que se encontrada à entrada da Báscula só se reflete na sua saída no flanco ascendente do clock (C de 0→1), ou no flanco descendente do clock (C 1→0). Elas podem ser sensíveis a qualquer dos flancos do clock.

As Básculas são as estalagens de que falámos no parágrafo sobre a Lógica Temporizada. Quando os bits são enviados a recolher as Letras para a Palavra que têm que transmitir, cada um deles tem tarefas muito distintas. Uns limitam-se a sair da estalagem e entrar logo na estalagem seguinte. Outros têm que visitar várias povoações, umas mais distantes outras menos, para conseguirem a Letra que pretendem e só depois chegam à estalagem seguinte. Mas a Palavra só faz sentido quando lidas em conjunto as Letras de todos os bits. Portanto é preciso fazer esperar os mais rápidos.

É aí que o dono da estalagem usa dos seus pergaminhos e deixa entrar todos os que chegam, mas só ao pôr do Sol ou ao nascer do Sol deixa que eles passem à sala que dá acesso à saída.

Se não existissem estas estalagens espalhadas pelas estradas do computador, os nossos bits passariam a vida muna correria desenfreada e sem rumo, nunca tendo pontos de referência para se encontrarem e juntarem as suas Letras.

Até ao fim de cada período de trabalho os bits têm que encontrar a próxima estalagem, sob pena de estragarem o trabalho dos colegas do grupo, pois a palavra vai ser ilegível.

Vamos deixar as estalagens e voltar às Básculas, as estalagens do computador.

São estas Básculas que, junto com a lógica temporizada, permitem a sincronização da atividade dos grupos de 8, 16, 32 ou 64 dos nossos amigos bits. O facto de não permitir que qualquer alteração no valor da entrada D durante o estado do clock em alta (C=1) se reflita na sua saída S, o que o Trinco D não consegue, faz da Báscula a ferramenta perfeita para a sincronização da informação que circula dentro dos circuitos do computador.

Foram as Básculas D a ferramenta posta à disposição da CPU para com a lógica temporizada poder organizar e sincronizar as informações que circulam num circuito do computador, para que num dado instante possa congelar uma determinada configuração de bits e processá-la.

Báscula D sensível ao flanco ascendente do Clock

Esta é a estalagem em que o dono só abre o acesso à saída ao nascer do Sol. Os clientes podem entrar a qualquer momento, mas ficam à espera dos restantes colegas do grupo. Só ao nascer do Sol podem passar à sala de saída, onde as Letras que transportam são lidas em conjunto e donde partem para o novo dia de atividade.

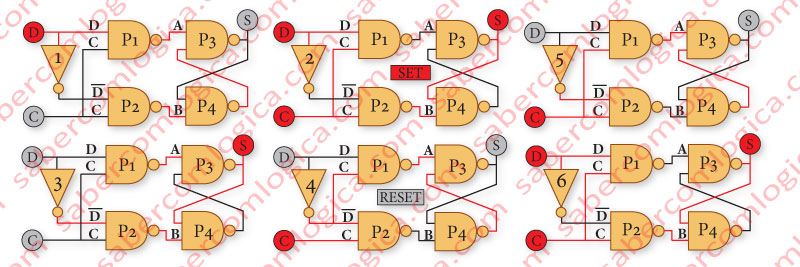

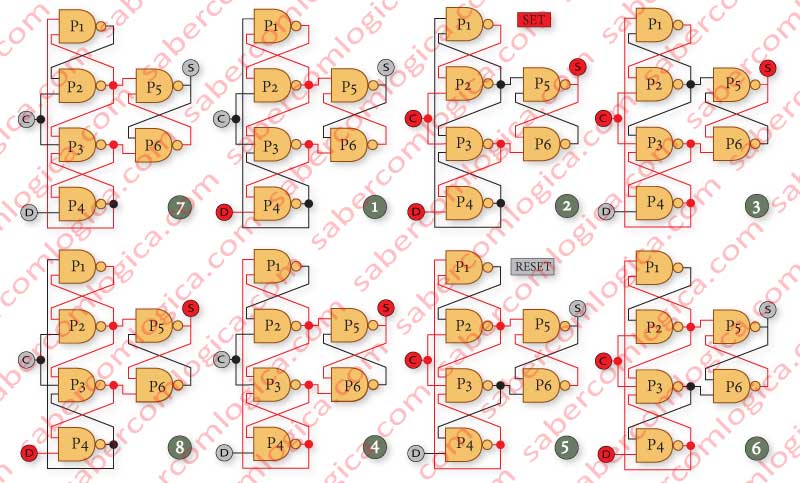

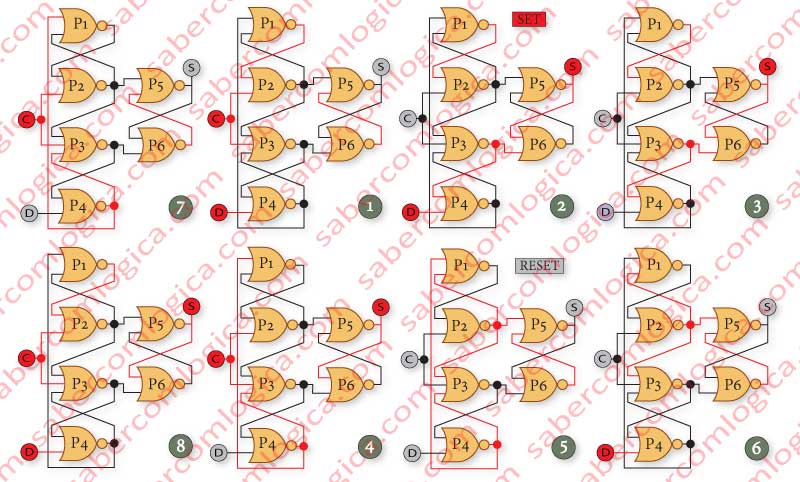

A Báscula D sensível ao flanco ascendente do Clock é constituída por 3 FFSR NAND [(P1/P2), (P3/P4) e (P5/P6)] interligados da forma que se pode verificar nos gráficos da Figura 5.

Evolução entre os Quadros 1→2 e 4→5 – C passa de 0→1 quando D=1 e S=0 ou quando D=0 e S=1. A passagem de C de 0→1 representa o flanco ascendente do clock. O valor de D é sempre colocado na saída S, que muda.

Evolução entre os Quadros 2→3, 3→2, 5→6 ou 6→5 – C está em alta (1), D passa de 1→0 ou de 0→1 e o valor de S, quer seja 0 ou 1, mantém-se inalterado. Podemos verificar que com o clock em alta (1), as alterações do valor de D não são refletidas na saída S, que se mantém inalterada.

Evolução entre os Quadros 3→4 e 6→1 – C passa de 1→0 quando D=0 e S=1 ou D=1 e S=0. A passagem de C de 1→0 representa o flanco descendente do clock. O valor de D nunca se reflete em S.

Evolução entre os Quadros 1→7,7→1,4→8 e 8→4– C está em baixa (0), D passa de 1→0 ou de 0→1. Com o clock em baixa (0) qualquer alteração do valor de D nunca é refletida na saída S.

Pudemos assim verificar que, nesta Báscula, toda e qualquer alteração no valor da sua entrada D só é refletida na saída S durante o flanco ascendente do clock C.

Báscula D sensível Ao flanco descendente do Clock

Esta é a estalagem em que o dono só abre o acesso à saída ao pôr do Sol. Os clientes podem entrar quando chegam, mas ficam à espera dos colegas do grupo. Só ao pôr do Sol são autorizados a passar à sala de saída, onde as Letras que transportam são lidas em conjunto e donde partem para novo dia de atividade.

A diferença entre esta estalagem e a anterior é de que, nesta os bits passam para a sala de saída e entregam as Letras para leitura ao fim do dia, enquanto na anterior o faziam no início do dia.

A Báscula D sensível ao flanco descendente do Clock é constituída por 3 FFSR NOR [(P1/P2), (P3/P4) e (P5/P6)] interligados da forma que se pode verificar nos gráficos da Figura 6.

Evolução entre os Quadros 1→2 e 4→5 – C passa de 1→0 quando D=1 e S=0 ou quando D=0 e S=1. A passagem de C de 1→0 representa o flanco descendente do clock. Nesta Báscula o valor de D vai-se refletir em S em qualquer das das situações.

Evolução entre os Quadros 2→3,3→2,5→6 e 6→5 – C está em baixa (0), D passa de 1→0 e de 0→1. Com o clock em baixa (0) qualquer alteração de D nunca é refletida na saída S.

Evolução entre os Quadros 3→4 e 6→1 – C passa de 0→1 quando D=0 e S=1 ou quando D=1 e S=0. A passagem de C de 0→1 representa o flanco ascendente do clock. Verificamos que nesta Báscula o valor de D não se reflete na saída S, que não muda.

Evolução entre os Quadros 1→7, 7→1, 4→8 e 8→4– C está em alta (1), D passa de 1→0 ou de 0→1 e o valor de S, quer seja 0 ou 1, mantém-se inalterado. Podemos verificar que com o clock em alta (1), as alterações do valor de D não são refletidas na saída S, que se mantém inalterada.

Pudemos assim verificar que, nesta Báscula, toda e qualquer alteração no valor da sua entrada D só é refletida na saída S durante o flanco descendente do clock C.

Registos

Registos são conjuntos de Básculas trabalhando em conjunto para os grupos de bits que temos referenciado. A quantidade de Básculas de cada Registo tem a ver com a largura dos Registadores da CPU, as memórias internas temporárias da CPU. Poderão ter 8, 16, 32 ou 64 Básculas conforme a CPU tiver capacidade de processar 8, 16, 32 ou 64 bits. É esta largura que define a quantidade de Básculas a utilizar em nos Registos a utilizar em todos os circuitos da CPU.

Conforme o tipo de Básculas com que são construídos poderemos ter Registos sensíveis ao flanco ascendente do Clock e Registos sensíveis ao flanco descendente do Clock.

Inicialização de um Registo

Por vezes vai ser necessário forçar as saídas de um registo a um estado de 0 ou 1 em todas as saídas, portanto em todas as básculas.

Caso de uma Báscula NAND

Podemos acompanhar esta situação nos dois gráficos da esquerda da Figura 7.

Os sinais CL e PR são ativos a 0. Porquê a 0?

Ambos os sinais estão inativos durante o funcionamento normal da Báscula. As portas NAND devolvem 1, se e só se todas as entradas forem 1. Assim, CL e PR estando a 1 deixam às outras entradas a escolha e respeitam a sua decisão.

Para forçar uma Báscula NAND a 0, processo a que se chama CLEAR, introduzimos o sinal CL nas portas P2,P4 e P6. Quando CL for 0 força nas mesmas o estado 1, o que corresponde a um RESET em todos os FFSR ou total na Báscula, cuja saída fica a 0.

Para forçar uma Báscula NAND a 1, processo a que se chama PRESET, vamos introduzir um sinal PR em cada uma nas portas P1,P3 e P5. Quando CL for 0 força nas mesmas o estado 1, o que corresponde a um SET em todos os FFSR ou total na Báscula, cuja saída fica a 1.

E porquê colocar o sinal à entrada dos três FFSR?

Porque se pretende criar uma situação estável que após a inativação do sinal não vá provocar um funcionamento inesperado da báscula.

Caso de uma Báscula NOR

Podemos acompanhar esta situação nos dois gráficos da direita da Figura 7.

Os sinais CL e PR são ativos a 1. Porquê a 1?

Ambos os sinais estão inativos durante o funcionamento normal da Báscula. As portas NOR devolvem 0, se e só se todas as entradas forem 0. Assim, CL e PR estando a 0 deixam às outras entradas a escolha e respeitam a sua decisão.

Para o CLEAR de uma Báscula NOR, introduzimos o sinal CL nas portas P1,P3 e P5. Quando CL for 1 força nas mesmas o estado 1, o que corresponde a um RESET em todos os FFSR ou total na Báscula, cuja saída fica a 0.

Para o PRESET de uma Báscula NOR, introduzimos o sinal PR em cada uma nas portas P2,P4 e P6. Quando PR for 1 força nas mesmas o estado 1, o que corresponde a um SET em todos os FFSR ou total na Báscula, cuja saída fica a 1.