Circuitos Integrados (Chips)

Para se obter o objetivo de replicar fisicamente o comportamento de uma porta lógica, os transístores têm de ser ligados em circuitos. Os primeiros circuitos foram construídos ligando os transístores com fios e posteriormente com linhas de cobre em placas chamadas circuitos impressos (mais para a frente falaremos sobre isto). Cada porta por sua vez podia ser ligada a outras da mesma forma. Era a integração de transístores em circuitos.

Conforme a complexidade dos circuitos evoluiu e a nanotecnologia começou a reduzir a dimensão dos transístores, os circuitos e os transístores passaram a ser construídos dentro do mesmo encapsulamento, isto é, de integração de transístores em circuitos passámos para circuitos integrados de transístores, ou Chips.

Os processadores são a forma mais conhecida de Chips em que atualmente se incorporam no mesmo encapsulamento e num circuito com perto de 1 cm² mais de 2 bilhões de transístores.

Vamos agora olhar para os transístores nMOS como interruptores e construir os circuitos elétricos que executarão fisicamente o comportamento das portas lógicas que são a visualização da abstração lógica dos operadores Booleanos. Mas antes, para que possamos entender bem como funciona um transístor, vamos verificar o processo de fabrico dum CHIP.

Fabrico de um CI com nMOS

Vamos agora analisar o processo de fabrico destes circuitos com transístores nMOS. O Circuito Integrado (Chip) começa por ser desenvolvido pelos engenheiros informáticos de acordo com a solução pretendida. Depois de projetado e desenhado, é decomposto nas várias máscaras que vão ser necessárias às várias fases da sua execução.

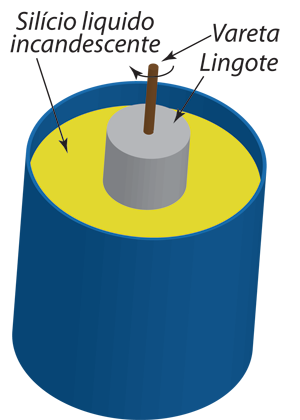

O wafer, termo inglês a que passaremos a dar a tradução em Português, a Bolacha, é o principal elemento usado na fabricação dos chips. É sobre a bolacha que vão ser implantados os transístores que irão dar origem ao Circuito Integrado. A bolacha “virgem” é feita de silício puro, que pode ser extraído da areia da praia e liquefeito a altas temperaturas.

Um pedaço de cristal de silício é colocado em uma vareta e então mergulhado nesse silício derretido. A vareta é suspensa e girada ao mesmo tempo, formando um grande cilindro de cristal de silício, também conhecido como lingote.

Um pedaço de cristal de silício é colocado em uma vareta e então mergulhado nesse silício derretido. A vareta é suspensa e girada ao mesmo tempo, formando um grande cilindro de cristal de silício, também conhecido como lingote.

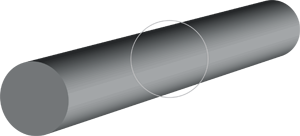

O lingote mede um a dois metros de comprimento e pode ter até 300 mm de diâmetro. O lingote é “fatiado” em bolachas (Wafers) e as bolachas seguem para produção.

Em cada bolacha são fabricados centenas de Circuitos Integrados (Chips) de microprocessadores do tipo i7, por exemplo, com mais de 700 milhões de transístores cada. Esta capacidade era possível graças à dimensão de 45 nanómetros já conseguida para cada transístor, que está agora nos 22 nanómetros.

Só para que se tenha uma ideia física do nanómetro, quando estiverem na praia peguem num grão de areia e imaginem toda a costa Portuguesa, cerca de 1.000 Km. É essa a relação entre 1 nanómetro e 1 metro.

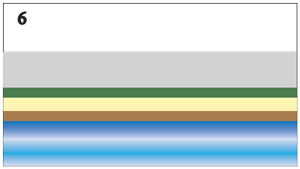

Quadro 1 – As bolachas retiradas do lingote de silicone são polidas e limpas de qualquer impureza. Esta é uma das partes críticas do processo.

Quadro 2 – De seguida procede-se à oxidação da superfície da bolacha. O dióxido de silício (SiO2) é um material muito estável e é utilizado como camada de proteção para a superfície ultra limpa da bolacha de silício, assim como camada isoladora. O SiO2 forma-se a altas temperaturas num forno de atmosfera oxigenada (oxidação a seco) ou ambiente de vapor (oxidação húmida). A este processo chama-se oxidação do silício. É como criar uma camada de ferrugem no ferro, só que muito mais rápido. O SiO2 é o principal componente do vidro, que se obtém pelo seu aquecimento a altas temperaturas.

Quadro 3 – Procede-se então ao bombardeamento e implantação de átomos de Boro no silício sobre toda a bolacha, duma forma extremamente uniforme, controlada e pouco intensa, por forma a que a camada P que se forma não seja muito intensa e seja regular. Os átomos de Boro provocam lacunas na estrutura dos átomos do silício (menos eletrões do que protões) criando assim a camada P (positiva).

Quadro 4 -Procede-se a novo bombardeamento com átomos de Boro, ainda menos intenso, com o fim de colocar a voltagem nas camadas superficiais no limiar do pretendido.

Quadro 5 -Porque uma das principais exigências deste processo é a extrema qualidade e limpeza das superfícies a trabalhar, de seguida remove-se a camada de dióxido de silício por um processo chamado de “etching”.

Etching consiste no ataque a um determinado elemento (a corrosão do elemento) por partículas em elemento liquido ou gasoso. Wet Etching que é químico ou dry etching que é feito em reatores de plasma.

Procede-se de novo à criação de uma fina camada de SiO2 totalmente renovada.

Segue-se a deposição de uma camada de polissílico seguida de outra de nitrato de silício (Si3N4). Esta deposição é feita em fornos a alta temperatura, por deposição de vapor de gás.

Tanto as camadas semicondutoras, como as condutoras e as isoladoras, podem ser formadas pela indução a altas temperaturas da deposição de gases selecionados. A deposição química de vapor pode produzir filmes sólidos de alta qualidade.

Tanto as camadas semicondutoras, como as condutoras e as isoladoras, podem ser formadas pela indução a altas temperaturas da deposição de gases selecionados. A deposição química de vapor pode produzir filmes sólidos de alta qualidade.

Quadro 6 – Procede-se à deposição de uma camada de produto fotossensível e resistente à ação dos agentes corrosivos do etching, sobre as outras.

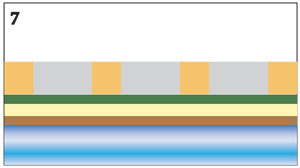

Quadro 7 – Por um processo de Fotolitografia procede-se à exposição da bolacha à luz ultravioleta, através das máscaras previamente desenvolvidas pelos engenheiros que projetaram o CI. A exposição do material fotossensível à luz ultravioleta altera as suas características, permitindo a sua remoção.

Quadro 8 – De seguida e por etching, removem-se as camadas de Si3N4 e polissílico nas zonas não protegidas pela camada fotossensível e resistente. Nessas zonas fica de novo exposto o SiO2.

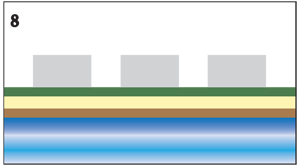

Quadro 9 – Procede-se então à exposição da bolacha a atmosfera oxidante e à consequente criação de uma camada muito mais espessa de dióxido de silício, que afeta o polissílico somente nos topos, não protegidos pelo nitrato de silício.

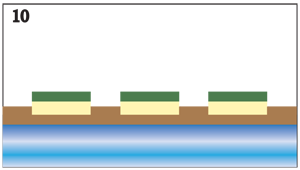

Quadro 10 – De seguida é removido o restante material fotossensível não exposto por um método exclusivo do próprio material.

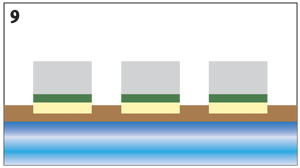

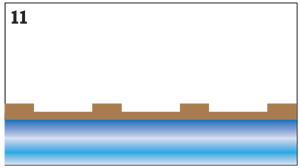

Quadro 11 – De novo pelo método de etching, são removidas as camadas de nitrato de silício e polissílico que agora se encontram desprotegidas. Posteriormente é removida uma pequena lâmina de dióxido de silício, também por etching, sendo de imediato reposta por oxidação, ficando assim superficialmente completamente limpa e renovada.

Quadro 11 – De novo pelo método de etching, são removidas as camadas de nitrato de silício e polissílico que agora se encontram desprotegidas. Posteriormente é removida uma pequena lâmina de dióxido de silício, também por etching, sendo de imediato reposta por oxidação, ficando assim superficialmente completamente limpa e renovada.

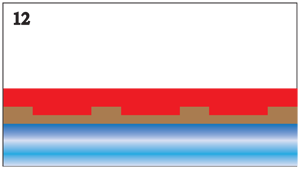

Quadro 12 – Imediatamente após a oxidação, uma camada de polissílico N dopado por bombardeamento com átomos de fósforo ou por difusão através do gás que origina a sua formação.

A adição de átomos de fósforo gera eletrões livres na estrutura do silício afetado.

A adição de átomos de fósforo gera eletrões livres na estrutura do silício afetado.

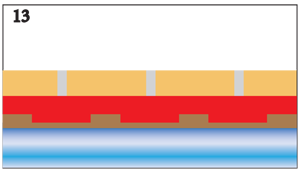

Quadro 13 – Procede-se de novo à deposição de uma camada do material fotossensível e a novo processo de fotolitografia, usando outras máscaras, que agora vão definir as portas dos transístores.

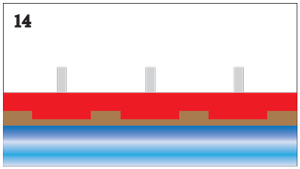

Quadro 14 – De seguida remove-se o material fotossensível exposto, deixando o polissílico exposto nessas zonas.

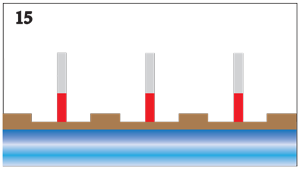

Quadro 15 – Por etching remove-se o polissílico exposto. Ficam assim definidas as portas.

Quadro 15 – Por etching remove-se o polissílico exposto. Ficam assim definidas as portas.

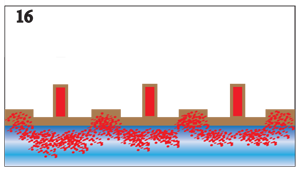

Quadro 16 – Esta figura compreende várias fases. Remoção do material fotossensível restante. Limpeza superficial por etching do dióxido de silício exposto. Criação de nova camada de dióxido de silício, que agora também protege as bases. Bombardeamento com átomos de fósforo ou arsénico. O arsénico nesta fase é preferível ao fósforo por permitir maior concentração superficial e um perfil mais equilibrado. Os átomos penetram através da camada mais fina de dióxido de silício mas são retidos e anulados pela sua camada mais espessa.

Quadro 16 – Esta figura compreende várias fases. Remoção do material fotossensível restante. Limpeza superficial por etching do dióxido de silício exposto. Criação de nova camada de dióxido de silício, que agora também protege as bases. Bombardeamento com átomos de fósforo ou arsénico. O arsénico nesta fase é preferível ao fósforo por permitir maior concentração superficial e um perfil mais equilibrado. Os átomos penetram através da camada mais fina de dióxido de silício mas são retidos e anulados pela sua camada mais espessa.

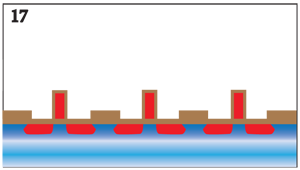

Quadro 17 – Cada processo de ionização deve ser seguido por um processo de recozimento a altas temperaturas, com o fim de reconstruir as estruturas cristalinas e incorporar os átomos implantados na estrutura cristalina. Devido à difusão os átomos de arsénio são adicionados à estrutura da bolacha

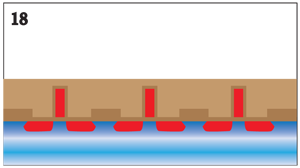

Quadro 18 -São necessários contactos para interconectar os dispositivos individuais e formar um CI. Para um melhor isolamento entre os transístores e as ligações em metal, uma camada de dióxido de silício é depositada.

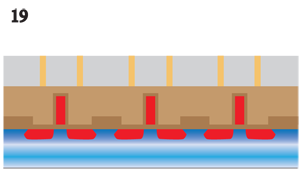

Quadro 19 – Procede-se de novo à deposição de uma camada de material fotossensível e através de mais um processo de fotolitografia expõe-se o mesmo através de uma máscara que define os pontos de ligação elétrica das fontes e dos drenos dos transístores.

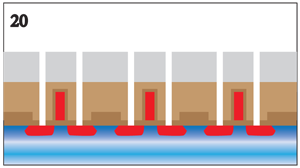

Quadro 20 – Remove-se o material fotossensível revelado. Através de etching remove-se o dióxido de silício que fica exposto, até aos poços de silício N dopado que define as fontes e os drenos dos transístores.

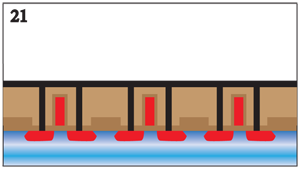

Quadro 21 – Coloca-se então uma camada de metal, p.e. alumínio, que vai preencher os furos abertos e estabelecer os contactos com as fontes e drenos dos transístores.

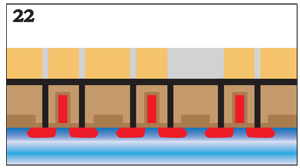

Quadro 22 – Mais uma vez coloca-se uma camada de material fotossensível que é exposto à luz ultravioleta de acordo com uma máscara que define um circuito elétrico ao nível desta camada. Nesta camada, pode haver noutros planos, contactos estabelecidos com bases que serão integrados no circuito definido por esta máscara.

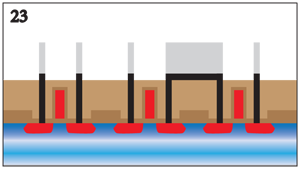

Quadro 23 – Remove-se o material fotossensível revelado e por etching remove-se o material metálico que fica exposto, removendo-se logo de seguida o material fotossensível sobrante. Fica assim definido um circuito elétrico que utiliza alguns ou todos os transístores antes fabricados. O circuito que vemos está só no plano em que temos o corte, mas as ligações são transversais e longitudinais ao longo de toda a bolacha.

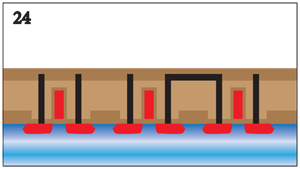

Quadro 24 – Em circuitos mais complexos podem ser necessárias várias camadas de ligações metálicas. No nosso caso vamos proceder a mais uma destinada ao circuito elétrico das portas dos transístores. Deposita-se uma camada espessa de dióxido de silício cujo fim é isolar todos os contactos estabelecidos até agora.

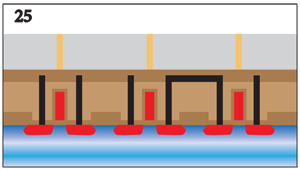

Quadro 25 – Deposita-se novamente uma camada de material fotossensível, um processo de fotolitografia com uma máscara que marca os pontos de contactos com as portas.

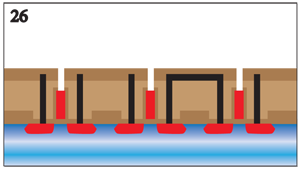

Quadro 26 – Remove-se a parte revelada do material fotossensível. Posteriormente remove-se por etching do dióxido de silício que fica exposto. Finalmente remove-se a parte restante do material fotossensível.

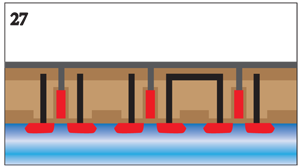

Quadro 27 – Coloca-se mais uma camada de alumínio que vai preencher todos os orifícios de contactos abertos desta vez.

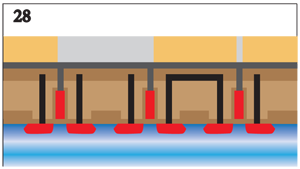

Quadro 28 – Coloca-se mais uma camada de material fotossensível sobre o alumínio e mais uma vez através de fotolitografia e de uma nova máscara com o desenho do circuito elétrico das portas dos transístores, expõe-se o material a luz ultravioleta.

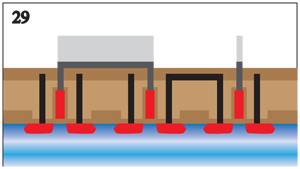

Quadro 29 – Limpa-se o material revelado. Por etching remove-se o metal nas zonas expostas. Remove-se a parte restante do material fotossensível. E temos pronto o circuito elétrico das portas dos transístores construídos. As ligações deste circuito estão a cinza para simbolizar que são executadas num plano diferente ao do corte em que estamos a trabalhar.

Quadro 29 – Limpa-se o material revelado. Por etching remove-se o metal nas zonas expostas. Remove-se a parte restante do material fotossensível. E temos pronto o circuito elétrico das portas dos transístores construídos. As ligações deste circuito estão a cinza para simbolizar que são executadas num plano diferente ao do corte em que estamos a trabalhar.

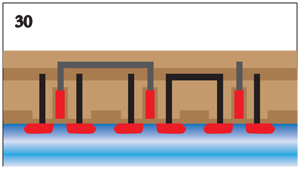

Quadro 30 – Como finalização deposita-se mais uma camada de dióxido de silício, que tem por fim isolar e proteger o chip.

E a bolacha está pronta. Daqui segue para o corte e separação de todos os chips fabricados, ligação dos seus terminais aos pinos e encapsulamento. Depois de passar por processos de teste e verificação, o Circuito Integrado (Chip) está pronto a entrar no mercado comercial.