COMO FUNCIONA UMA SDRAM

OS COMANDOS

Uma memória SDRAM, aquela de que vimos falando como Memória Principal, funciona obedecendo a comandos que o CM (Controlador de Memória) lhe envia sob a forma de combinação dos sinais que lhe são fornecidos. Os comandos são as mnemónicas de um certo Opcode a que correspondem determinados valores dos sinais que são enviados ao módulo e por sua vez aos DIE.

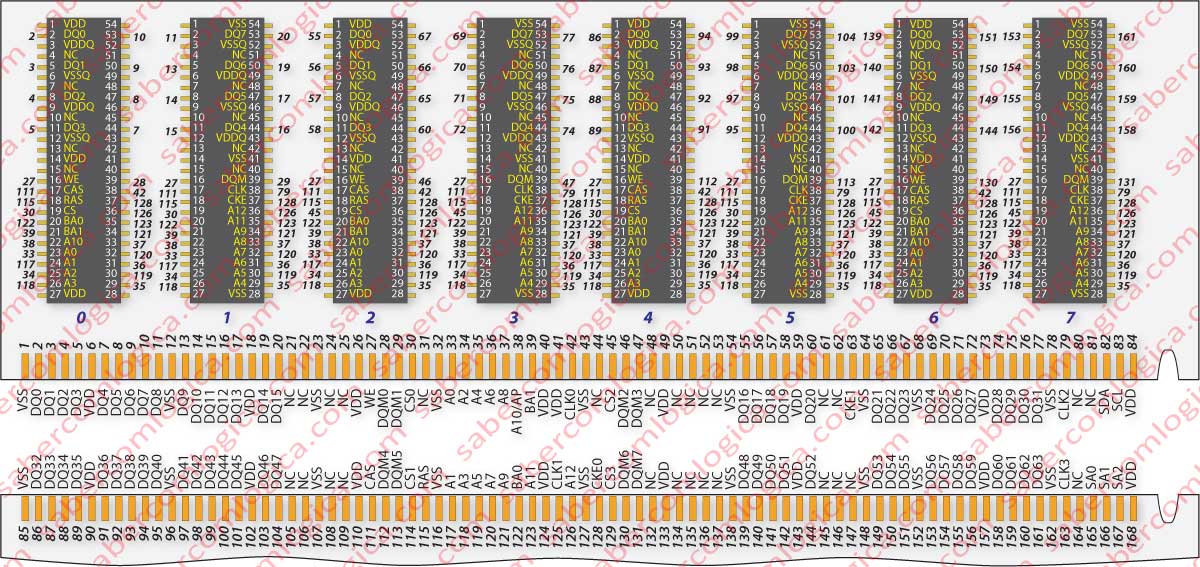

Vamos esquecer a nossa pequena memória e olhar para um módulo de memória de 256 MB, composto por 8 Dies de 256 Mb, cada um composto por 4 Bancos de matriz quadrada de 8.192 linhas por 1.024 x 8 = 8.192 colunas cada.

DIMM ou módulo de memória SDRAM de 256 MB, composto por 8 Dies de 256 Mb de 4 Bancos de matrizes de 8192 linhas por 1024 x 8 colunas. Estão identificados e correlacionados os contactos do DIMM com os pinos dos Dies de interesse relevante.

Comecemos por observar o esquema do DIMM correspondente a este módulo, com as ligações correspondentes aos seus contactos e a sua correspondência na ligação aos oito Dies, conforme descriminado no gráfico da Figura 19. Verificamos que:

- Os contactos de endereços A0 a A12, os contactos de I/O DQ0 a DQ63, os contactos dos sinais RAS, CAS, WE, AP, CKE0, BA0 e BA1, ligam a todos os DIEs;

- Os contactos dos sinais CS0 e CS2, CLK0 e CLK2, ligam aos DIEs 0 a 3 e 4 a 7 respetivamente;

- Os contactos dos sinais DQM0 a DQM7 ligam aos Dies 0 a 7, respetivamente um a cada;

- Os contactos dos sinais CKE1, CS1, CS3, CLK 1 e CLK3 não são utilizados nestes DIEs;

- Os contactos dos sinais SA0, SA1, SA2, SDA e SCL são específicos de uma ROM do DIE chamado SPD (Serial Presence Detection).

Já descrevemos todos estes contactos anteriormente. Os últimos sinais referidos são os contactos de comunicação da SPD (Serial Presence Detection), uma Rom cuja função é identificar o tipo do DIMM, a organização da SDRAM e os seus parâmetros de tempos perante o CM (Controlador de Memória) que, com base nessas informações, lhe irá enviar os comandos.

Falta-nos ainda referir as várias funções do sinal AP, que se encontra no pino A10 e que podem ser:

- Se a memória estiver em modo de leitura ou escrita

- Se o endereço enviado disser respeito a uma linha AP tem o significado do bit desse endereço.

- Se o endereço enviado disser respeito a uma coluna então:

- Se AP estiver em alta, o precarregamento é iniciado de imediato após a conclusão da rajada.

- Se AP estiver em baixa o comando de precarregamento deve ser executado separadamente para que o precarregamento se efetue.

- Se a memória estiver em modo de precarga

- Se AP estiver em alta todos os bancos devem ser carregados,

- Se AP estiver em baixa só será carregado o banco selecionado por BA0 e BA1.

Uma memória SDRAM pode ter vários modos de operação, que são:

Modo de escrita ou leitura, que como o nome diz é o modo em que se encontra quando se fazem acessos de escrita ou leitura à matriz de dados.

Modo de precarga, o modo em que se encontra quando se está a fazer uma operação separada de precarga.

Modo de registo, o modo em que a memória se deve encontrar quando nos bits de endereço o CM lhe envia vários parâmetros de execução, como já veremos de seguida.

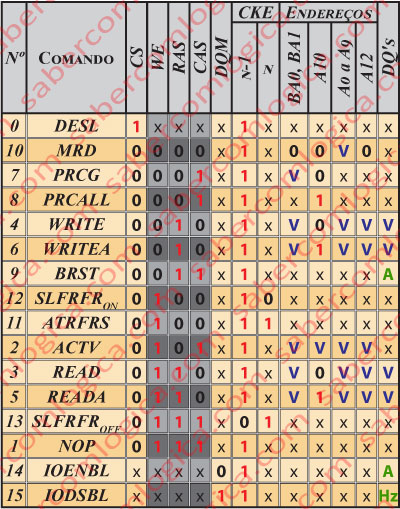

Vamos então passar à identificação dos comandos que são enviados à SDRAM, junto com uma tabela dos valores dos diversos sinais, inclusive a evolução de CKE do estado anterior para aquele que visa a instrução, conforme o descrito na Figura 18:

0. DESL (DESeLect) – Inibição de Comandos – Este comando torna inativos todos os sinais de comando enviados à memória, não prejudicando no entanto todas as operações que se encontrem em curso. Atua através de CS que, ativo em Baixa (0) impede o sinal de clock

Tabela de valores de diversos sinais nos pinos dos DIE para os comandos enunciados. Legenda: 0 – Em baixa; 1- Em alta; V – Válido com seu valor; A – Activo; Hz – Em alta impedância; x – Não interessa (qq valor)

de provocar a memorização no registador de sinais.

1. NOP (No OPeration) – Sem Operação -Mantém a memória ativa e pronta para receber sinais mas sem efetuar qualquer operação.

2. ACTV (ACTiVe)- Banco Ativo – Este comando seleciona um Banco através do valor dos sinais BA0 e BA1 e ativa uma linha através dos sinais de endereço de linha (RAS ativo) fornecidos por A0 a A12. A linha mantém-se ativa até que surja um comando de Precarga. Não pode ser aberta outra linha até que um comando de Precarga seja efetuado.

3. READ – Leitura – Este comando inicia uma leitura em rajada no Banco selecionado por BA0 e BA1 e na coluna indicada pelos sinais A0 a A9. Nesta instrução o sinal A10 fornecido no endereço tem por função indicar se a forma como é feita a Precarga. Por isso passa a assumir a designação AP (Auto Precharge). Este comando é sem Precarga automática, o que é indicado pelo sinal AP em baixa (0).

4. WRITE – Escrita – Este comando inicia uma escrita em rajada no Banco selecionado por BA0 e BA1 e na coluna indicada por A0 a A9. AP (correspondente a A10) nesta instrução está a 0, pelo que a escrita é feita sem Auto Precarga.

5. READA – Leitura com Auto Precarga – Idêntico ao comando READ, com a diferença que, neste caso AP está em alta (1), pelo que, no final da rajada, é executado um comando de Precarga automaticamente.

6. WRITEA – Escrita com Auto Precarga – Idêntico ao comando WRITE, com a diferença que, neste caso AP está em alta, pelo que, após terminar a rajada é executado um comando de Precarga automaticamente.

7. PRCG (PReCharGe) – Precarga no Banco selecionado – Este comando fecha a linha ativa e inicia uma Precarga no Banco ativo. Neste comando o sinal AP tem um significado diferente. AP determina se a Precarga se dirige ao Banco ativo ou a todos os Bancos a carregar. No caso deste comando, AP está em baixa (0), pelo que só o Banco ativo será Precarregado.

8. PRCALL (PReCharge ALL) – Precarga de todos os Bancos – Idêntico ao comando anterior, sendo que, neste caso AP está em alta (1), o que indica que a Precarga será feita a todos os Bancos.

9. BRST (BuRSt Terminate) – Término de Rajada – Este comando tem por fim interromper uma rajada de leitura ou de escrita de qualquer dimensão, no momento em que é executado. Quando executado este comando, a Precarga não é efetuada caso esteja em leitura ou escrita com auto precarga. Deverá portanto ser sempre executado um comando de Precarga após este e antes da abertura de qualquer outra linha.

10. MRD (Mode Register Definition) – Definição do Modo de Registo – O Modo de Registo corresponde a um estado da memória em que são memorizados vários parâmetros de operação que lhe são fornecidos pelos valores do endereço A0 a A11. A12 deve ser mantido em baixa (0). Antes deve ser estabelecido o funcionamento da memória em Modo Registo, o que será feito pela combinação de sinais da tabela da Figura 18. Todos os Dies devem estar em modo de inibição de comandos e só após decorrido o tempo necessário à definição do Modo de Registo poderá ser efetuado qualquer outro comando sobre a memória.,

11. ATRFRS (AuTo ReFReSh) – Refrescamento Automático – Este comando efetua um refrescamento de todas as células da memória. No caso desta memória corresponde a 8.192 ciclos de refrescamento em sequência, por cada intervalo de tempo predefinido. É precisamente este comando que garante que o valor contido dentro dos condensadores é preservado antes que o balde se esvazie a ponto de esse valor já não poder ser reconhecido.

12. SLFRFR ON (SeLF ReFResh ON)- Refrescamento autónomo ligado – Este comando é utilizado quando se pretendem preservar os valores contidos na memória, mesmo quando o sistema é colocado em StandBy. É ativado da mesma forma que o Auto Refresh, só que neste caso o valor de CKE é colocado em baixa (0). Ao ser iniciado, a memória ativa o seu Clock interno, com o qual vai executar os tantos ciclos de Auto Refresh quantos os necessários, enquanto se mantiver no estado de Self Refresh.

13. SLFRFR OFF (SeLF ReFResh OFF)- Refrescamento autónomo desligado – Para sair deste estado são necessários vários comandos numa determinada sequência e o DIE deve ser de imediato colocado em Inibição de Comandos, antes de ser efetuado qualquer outro comando.

14. IOENBL (Input Output ENaBLe) – Permissão de Entrada/Saída – Este comando corresponde à manutenção do DQM do DIE em baixa (0). Como se viu o DQM de cada DIE é comandável autonomamente, pois existe no DIMM uma entrada para cada um (DQM0 a DQM7).

15. IODSBL (Input Output DiSaBLe) – Inibição de Entrada/Saída – Este comando corresponde à colocação do respetivo DQM em alta (1), o que coloca os buffers em alta impedância, impedindo assim a entrada ou saída de qualquer dado no DIE.

LATÊNCIA

As memórias Dinâmicas têm definidos tempos de espera para que algumas funções se possam cumprir. Esses tempos, a que chamamos latência, têm normalmente a ver com o tempo de espera para que o estado de um circuito se equilibre.

Se tivermos um carreiro estreito e de repente o enchermos com água por um dos lados, verificamos que, antes que a água estabilize dentro do carreiro para que a possamos medir, vai formar ondas que correm de um lado para o outro.

Com os circuitos elétricos, embora a outra escala, tudo se passa da mesma forma. Na realidade, o carreiro é o condutor elétrico em estado indefinido e a água são os eletrões.

Quando se despeja uma enorme quantidade de eletrões para dentro de um condutor, há que aguardar algum tempo para que o seu estado estabilize num valor definido. Com o fim de evitar erros resultantes da leitura do estado de um circuito não estabilizado, os fabricantes de memórias definiram um conjunto de tempos a respeitar entre os diferentes comandos que se mandam executar na memória.

OS TEMPOS

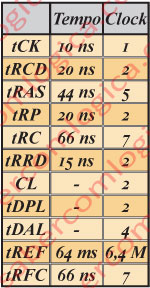

Os tempos são inicialmente definidos em nanossegundos e depois traduzidos em ciclos de clock, conforme a frequência do DIMM de SDRAM.

Por hábito traduzem a quantidade de ciclos como sinal de qualidade. Quanto menos melhor. Mas não é assim. Quanto menos, menor o número de ciclos de clock necessários para preencher o valor em nanossegundos, menor a frequência da SDRAM.

Em nanossegundos, desde as primeiras SDRAM até agora às mais modernas DDR3 SDRAM, as melhoras que se conseguiram rondam uma redução próxima de 50%.

De entre uma enorme quantidade de tempos que não é objetivo deste trabalho descrever, vamos analisar aqueles mais notórios e que podem intervir na continuação do nosso trabalho.

tRCD – RAS to CAS Delay – Representa o número de ciclos de Clock que decorrem desde a ativação de uma linha até ao comando de leitura dos dados (ativação de CAS). É o tempo necessário para o SA (Sense Amplifier) detetar a carga na célula de memória, restaurá-la e aguardar a estabilização dos sinais.

tRAS – Activate to Precharge Comand – Representa o número de ciclos de Clock decorridos desde a ativação de um Banco até ao início da operação de Precarga.

tRP – RAS Precharge – Representa o número de ciclos de clock decorridos durante a operação de precarga (desativação da linha e carregamento das BL). É o tempo necessário para carregar as BL na totalidade da sua capacitância, curto circuitá-las para ficarem perfeitamente equilibradas e aguardar a estabilização dos sinais.

tRC – Active to Active Comand Period – Representa o tempo mínimo a decorrer entre a ativação de diferentes linhas no mesmo banco.

tRRD – Active Bank a to Active Bank b – Número de clocks mínimo entre ACTV em bancos diferentes.

CL – CAS Latency – Número de clocks entre a ativação do sinal CAS e a disponibilização estável dos dados nos DQ do DIMM. É o tempo necessário para o BT ampliar e estabilizar o sinal que sai das linhas de um circuito integrado de dimensão nanométrica para as linhas do circuito impresso do DIMM, até estar estável nos seus pinos DQ.

tCK – Clock Cycle Time – Representa o período de tempo associado à frequência de operação do barramento de memória.

tRFC – Refresh Row Cycle Time – Representa o tempo mínimo de duração de um comando de autorefresh, ou seja o tempo de refrescamento de uma linha.

tREF – Refresh Period (8.192 linhas) – Representa o período máximo de tempo entre processos de autorefresh, ou ainda o tempo máximo que uma linha se pode manter sem refrescamento.

tDAL – Last Data In to Active delay – Tempo mínimo entre o último dado lido dos DQ e novo comando Active.

tDPL – Last Data In to Row Precharge – Tempo mínimo de espera desde o último dado lido dos DQ e um comando PRCG.

Tabela com os valores em nanossegundos e ciclos de clock para os tempos de uma memoria SDRAM de 100 MHz

Vamos agora enumerar os diversos procedimentos que completam, por exemplo, uma operação de leitura num DIE já selecionado, isto é, com CS em baixa.

- Ativação de banco, linha e SA (Sense Amplifiers).

- Tempo de espera para identificação do valor nas células.

- Comando de leitura. Ativação de coluna para início de rajada.

- Tempo de espera para amplificação e estabilização dos sinais nos DQ.

- Desativação de linha de endereço, desligar o SA da alimentação, ligar os transístores PRE (T5) e precarga do banco.

- Tempo de espera para carga, equilíbrio e estabilização das linhas de bit na sua máxima capacitância.

- Ativação de nova linha.

Vamos traduzir isto em tempos e ciclos de clock na tabela da Figura 23, de acordo com as especificações de uma memória SDRAM de 100 MHz e com uma CL (CAS Latency) de 2 ciclos de clock. O valor de CL em ciclos de clock depende da frequência do barramento da memória e do tempo que ela necessita para a estabilização dos sinais nos DQ, sendo definido pelo CM (Controlador de Memória) aquando da definição dos parâmetros em modo de registo, MRD. Todos estes tempos são comunicados ao CM pelo SPD dos DIEs.

É com base no conhecimento dessas características que o controlador de memória determina quando deve enviar os comandos para os pinos do DIMM, por forma a que sejam sempre respeitados os tempos mínimos específicos do DIMM para todos os comandos.

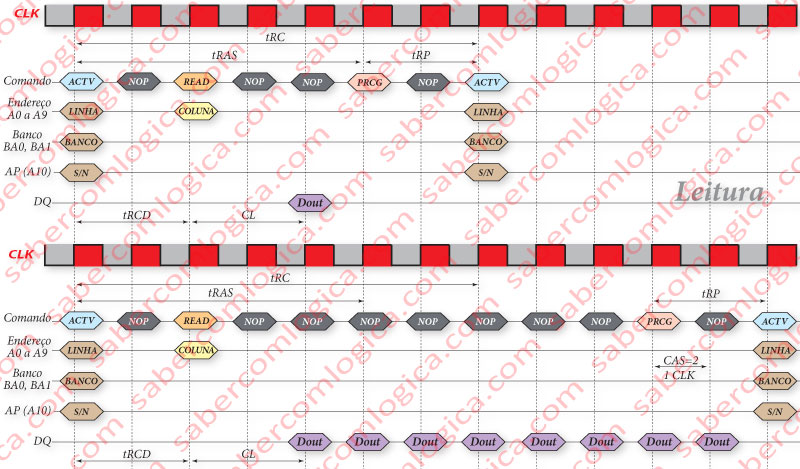

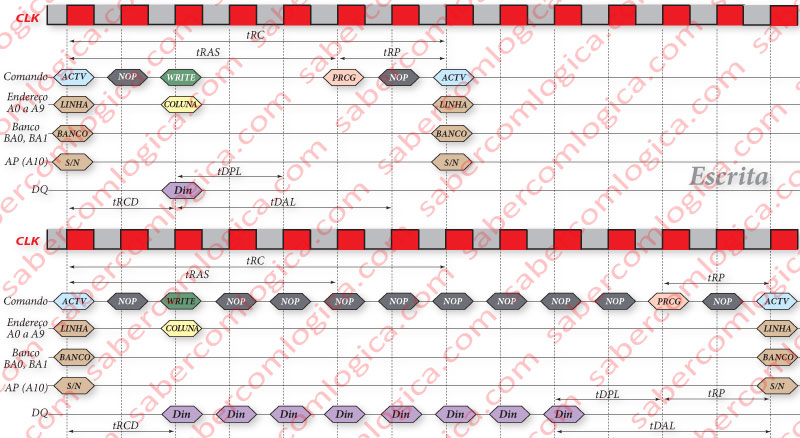

Gráfico dos tempos de uma operação de leitura. Em cima leitura sequencial em linhas diferentes. Em baixo 8 leituras em rajada na mesma linha

Nas Figuras 22 e 24 elaborámos gráficos com a evolução dos sinais com o clock durante uma leitura e uma escrita. Os comandos, os inputs de dados, de endereços e de sinais e os outputs de dados, aparecem como pequenos hexágonos irregulares sobre o comprido, algures durante o ciclo de clock em que vão ser assumidos pela SDRAM.

Já vamos entender o porquê da forma e do local onde aparecem, porque não são assim só por uma questão gráfica.

Na parte superior do gráfico está a representação de um acesso simples a uma linha, com toda a composição do ciclo devidamente quantificada, sendo que outro acesso seguido a outra linha do mesmo banco será a repetição deste ciclo com os mesmos tempos.

Gráfico dos tempos de uma operação de escrita. Em cima um escrita. Em baixo 8 escritas em rajada na mesma linha.

LEITURA (READ E READA)

No final da leitura temos que considerar a latência CL, para dizermos que a precarga pode começar depois de tRAS mas nunca mais cedo do que:

- 1 ciclo de clock antes do último dado a ler quando CL for 2.

- 2 ciclos de clock antes do último dado a ler quando CL for 3.

Mas assim vão-se destruir dados, pois um dado está a ser lido nesse ciclo e outro vai ser lido no ciclo seguinte. Carregando as BL ( Bit Line), o valor a ser lido vai-se alterar, não?

O último dado lido já foi colocado no trinco aquando do comando READ e as células estiveram a refrescar até ao fim da rajada, pois o SA esteve ligado.

O dado está protegido no trinco até ao próximo clock, que só se dará quando um comando READ acontecer. Precisa agora do tempo CL até poder ser lido nos DQ, mas isso já não tem nada a ver com o que se passa nas células da matriz.

De qualquer forma há que verificar sempre se tRAS está a ser respeitado, pois a precarga nunca poderá ser iniciada antes de cumprido este tempo.

No caso de um comando READ (leitura sem auto precarga), o CM encarrega-se de fazer estes cálculos e verificações e envia o comando PRCG na ocasião certa.

Já no caso de um comando READA (leitura com auto precarga), em que o sinal PRCG é despoletado pelos circuitos internos da memória, ambos tRAS e CL após a última leitura têm que ser tidos em conta para a determinação do momento de o fazer.

Na Figura 22 podemos verificar que, na parte superior (leitura isolada – rajada de 1) é o tempo tRAS (5 CLK) quem determina o início da precarga pois é superior a tRCD (ponto em que o comando READ é emitido) mais 1 CLK (ponto em que o comando PRCG pode ser emitido).

Já na parte inferior,caso da rajada de 8 leituras seguidas, tRAS é largamente ultrapassado e portanto PRCG pode ser emitido no momento certo, isto é, 1 ciclo de clock antes da leitura do último dado em DQ.

Na leitura isolada gastam-se 7 ciclos de clock para ler um dado, o que é precisamente o valor de tRC. Na leitura em rajada gastam-se 12 ciclos de clock para obter 8 dados.

Torna-se assim fácil entender o recurso a leituras em rajada. Mas só depois de passarmos pelo entendimento das memórias cache, a vantagem deste processo em que se leem dados em proximidade que não estão a ser pedidos será bem entendida.

ESCRITA (WRITE E WRITEA)

Na escrita não há latência CAS. Isto significa que, uma vez colocados os valores vindos do exterior nos DQ, os mesmos podem ser de imediato lidos pela memória através de um comando WRITE ou WRITEA.

No entanto, quando um comando WRITE ou WRITEA acontece, abrem-se as comportas para o circuito interno da memória, que vai demorar o tempo tDPL a estabilizar e a registar esses valores nos condensadores.

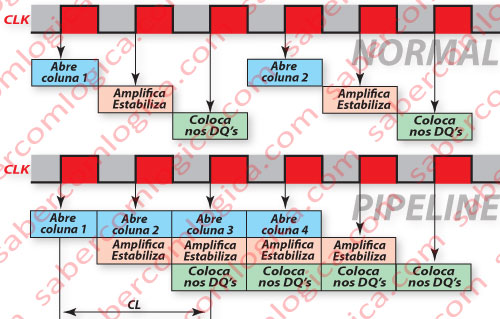

Pipeline

Só depois de decorrido tDPL, o comando PRCG que vai fechar a linha e curto circuitar e encher as BL pode ser efetuado, devendo também aguardar um tempo tRP até que se possa efetuar um comando ACTV para ativar outra linha e recomeçar o processo.

Ao conjunto destes dois tempos chama-se tDAL (tDPL+tRP), que é o tempo que medeia entre a leitura do último dado dos DQ e a ativação de uma nova linha.

As memórias SDRAM, porque vêm concebidas para leitura e escrita por rajada, dispõem da possibilidade de executar este processo em pipeline, ou seja, em paralelo.

Veja-se a Figura 26. É assim que a SDRAM consegue garantir um dado por cada ciclo de clock, nos DQs.

MAIS SOBRE LÓGICA TEMPORIZADA

Prometemos há pouco esclarecer a razão da forma e localização dos sinais. Vamos então a isso.

Como se sabe, nada no nosso mundo é instantâneo. Embora ao nível das nossas dimensões assim possa parecer, efetivamente não é. Tudo é mensurável, em unidades a que não somos sensíveis, mas a que um computador é.

A passagem de um sinal em alta para um sinal em baixa e vice-versa, não é instantânea. Há um tempo necessário para que o sinal se mantenha estável e um tempo mínimo para a sua leitura poder ser exata.

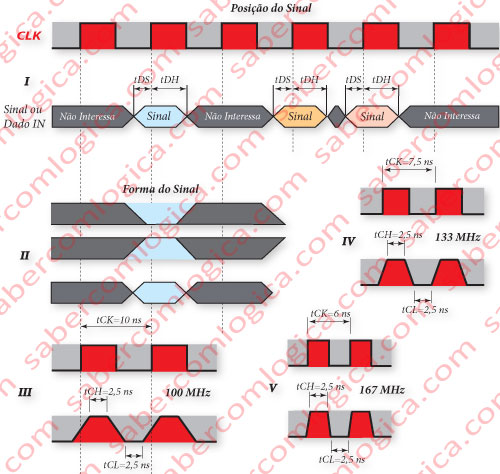

Ora, a forma do sinal resulta precisamente destas possibilidades de transição e das suas sobreposições, como se pode ver na Figura 27, cujos quadros nos vão servir de apoio.

E a sua colocação em relação ao sinal de clock tem a ver com os tempos que os fabricantes de memórias definiram como ideais para o sinal ser colocado antes do flanco ascendente do clock e por quanto tempo deve ser mantido a partir daí.

A esses tempos, definidos nas características da memória para cada sinal e para cada input, vamos dar um nome comum, que torna mais fácil o entendimento. Assim:

tDS – Data In Setup Time – Tempo mínimo para o sinal ser colocado nos pinos antes do flanco ascendente do clock em que se pretende que seja assumido.

tDH – Data In Hold Time – Tempo mínimo por que o sinal deve ser mantido estável após o instante do flanco ascendente do clock.

Mais 3 sinais aparecem como novos nessa figura, que significam:

tDK – Tempo em que a mesma posição do clock se repete, o que resulta da frequência de vibração do circuito.

tCH – Tempo em que o clock se deve manter em alta.

Forma e posição dos sinais

tCL – Tempo em que o clock se deve manter em baixa.

No Quadro I podemos ver a localização dos sinais relativamente ao flanco ascendente do clock, definida pelos tempos tDS e tDH.

No Quadro II podemos ver como se adquire a forma final do sinal. Ele tanto pode evoluir de alta para baixa como na primeira linha, como de baixa para alta na segunda linha.

A terceira linha é a combinação das duas, englobando todas as hipóteses, aquela que é apresentada no Quadro I.

No Quadro III temos a evolução real do sinal de clock. Nada é instantâneo. Definidas as larguras do tempo de clock em alta e em baixa, o restante é dividido pelos flancos ascendente e descendente.

Nos Quadros IV e V vemos a forma cada vez mais quadrada da onda do sinal de clock. Conforme a frequência aumenta, diminui tCK, mantendo-se os valores dos tCH e tCL, como por definição acontece para todas estas frequências de memória