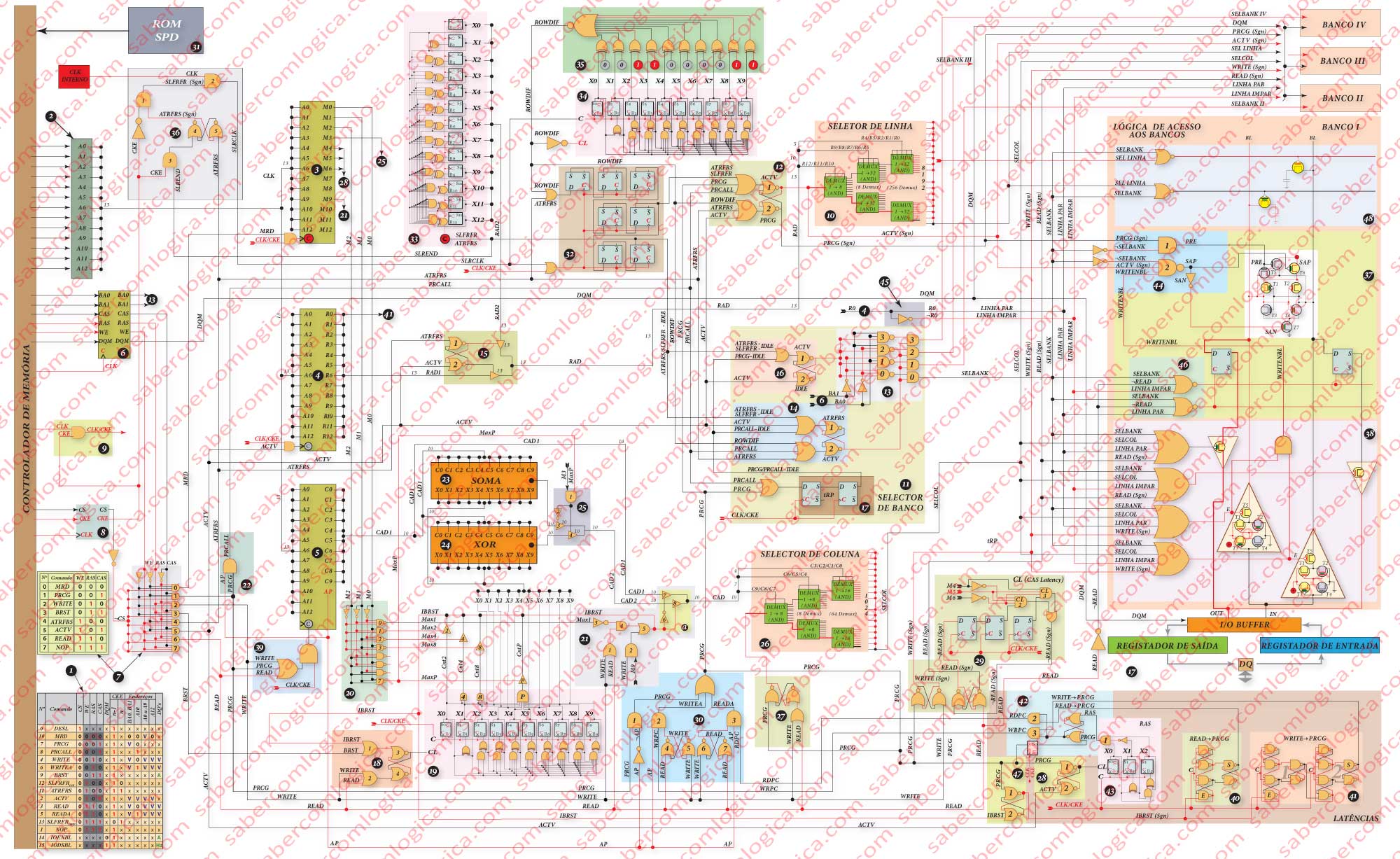

O COMANDO DE UMA SDRAM

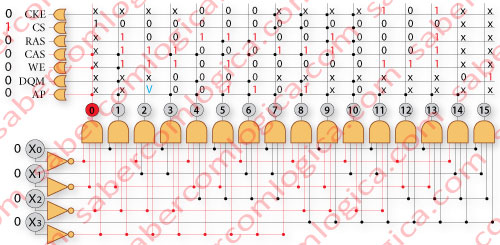

DIAGRAMA DE COMANDO

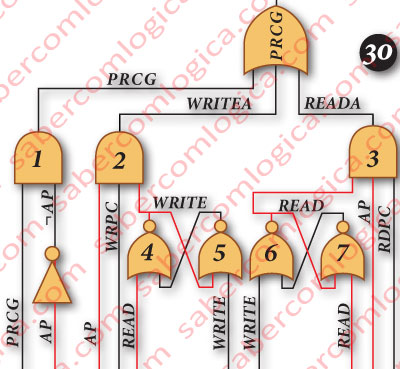

Na Figura 30 vamos tentar desenhar um diagrama lógico que ilustre passo a passo a forma como os comandos que o CM envia à memória são reconhecidos e executam as funções que lhes competem.

Qualquer comparação com a realidade é pura coincidência, como dizem os produtores cinematográficos. É um circuito didático cuja construção se baseia simplesmente em raciocínios lógicos e nos conhecimentos que nos são proporcionados pelos fabricantes de memórias SDRAM, com propósitos e objetivos completamente diferentes dos circuitos comerciais.

O nosso objetivo é tornar evidente como tudo funciona com zeros e uns, com recurso à utilização de operadores lógicos que, inseridos em circuitos realizam os nossos raciocínios lógicos.

Nas designações dos bits em endereços, contadores e outros, independentemente da direção como se encontrem representados (de baixo para cima, de cima para baixo, da esquerda para a direita ou da direita para a esquerda), a ordem dos bits é sempre a do número que segue a letra.

Assim, em A0….A12 ou em A12….A0, A0 representa o bit de menor ordem e A12 o bit de maior ordem. Tudo tem a ver com conveniência de representação gráfica de todo o conjunto.

Vamos distinguir comandos exercidos num pulso de clock de sinais contínuos em que aqueles serão convertidos para que o registo da passagem do comando permaneça. Os comandos convertidos em sinais levarão à frente a designação (Sgn). Aqueles que só existem num estado devem-se entender como sinais.

Porque entendemos ser mais eficaz ao entendimento do diagrama a representação dos comandos ativos em alta, devido à sua atuação como SET ou RESET nos FFSR (Flip Flop Set Reset) optámos por essa forma de representação, fazendo a sua passagem para baixa nos locais próprios sempre que intervêm em comandos convencionais da memória, como Write ou Read, por exemplo.

O diagrama da Figura 30 é apresentado no final da descrição. As referências do tipo (x) referem-se a quadros assinalados como notas nesse diagrama. Vamos introduzindo localmente Figuras representativas desses quadros.

CONTROLADOR DE MEMÓRIA (CM)

O CM encarrega-se:

- de mandar executar à memória todas as operações de escrita e leitura que lhe são pedidas pela MMU (Memory Management Unit).

- da precarga no seguimento a uma operação de escrita ou leitura,

- da precarga isolada de um ou de todos os Bancos,

- do refrescamento das células da memória dentro dos períodos definidos e

- de tudo o mais que veremos adiante.

Quando um DIMM é ligado a um CM, ou quando um computador arranca, o DIMM, através do chip SPD (Serial Presence Detection), identifica-se perante o CM, fornecendo-lhe todos os parâmetros de que necessita para poder executar todos os comandos.

A partir desta informação o CM sincroniza o seu clock para o DIMM com a frequência de vibração que por ele lhe foi indicado e passa a enviar ao DIMM o sinal de clock dos circuitos internos da memória.

O CM terá que funcionar com vários valores de frequências de sinais de clock.

Por exemplo, no caso das evoluções DDR, DDR2 e DDR3 da SDRAM, o clock do barramento de ligação à memória é diferente do clock interno da memória, pois vários conjuntos de dados (até 8) são enviados pelo barramento durante o mesmo ciclo de clock da memória, ou quando o CM é interno ao chip da CPU, o clock com que se liga à MMU, embora com frequências diferentes da CPU é muito diferente dos já mencionados, como por exemplo no caso do i7 Nehalem da Intel, que veremos como caso de estudo no final do Capítulo sobre a Cache.

Com base no valor de clock que entretanto criou para o DIMM e nos tempos que lhe foram pelo mesmo fornecidos, o CM vai criar a Máquina de Estados que vai gerir clock após clock o sinal que é enviado em cada ciclo, de forma a cumprir todos os parâmetros desse DIMM.

Máquina de Estados? O que é isso?

“Máquina de Estados é um circuito que transita entre vários estados de acordo com a transição do clock e com a tabela de estados, que indica para cada estado e combinação dos valores de entradas, qual o valor das saídas e qual o estado para que a máquina transita no clock seguinte.”

“Um Estado é uma situação estável de um circuito que só evolui quando o sinal de relógio fizer evoluir as básculas que ao mesmo são sensíveis”.

O CM é uma Máquina de Estados, que vai fazendo evoluir os sinais que coloca nos pinos de acordo com os tempos e as características do DIMM.

Como vimos nos gráficos elaborados para ilustrar os tempos, os sinais de comando são enviados pelo CM ao DIMM em ciclos de clock definidos, sob a forma de impulsos com a duração tDS+tDH. No intervalo entre esses sinais de comando o CM envia sinais NOP.

Mas, no período entre dois sinais de comando, em que o CM só envia sinais NOP, como por exemplo na parte inferior do gráfico da Figura 22, o circuito interno da memória deve manter o estado gerado pelo impulso referente ao sinal de comando que recebeu até à chegada de outro diferente.

Com esse propósito usámos o Flip Flop SR, que memoriza um valor pulsado em alta em qualquer uma das suas entradas e só muda quando receber outro pulso em alta na entrada oposta. Vamos passar a designá-los por FFSR.

Escolhemos FFSR com portas NOR porque estes não alteram o seu estado perante duas entradas a 0.

O SET e o RESET dos FFSR será sempre efetuado por comandos que se mantêm ativos durante um ciclo de clock. Nunca haverá dois comandos ativos em simultâneo, mas os dois comandos que ligam a um FFSR vão estar simultaneamente inativos. Como nós não queremos que as saídas sejam alteradas por esse facto, escolhemos FFSR com portas NOR.

Vamos assumir que o CM tem os seus 16 sinais definidos sob a forma de opcodes (0 a 15), conforme descrito na Figura 18, constantes também da tabela da Figura 30 (1). Assim, quando o CM quer enviar um comando ao DIMM, envia o respetivo opcode ao circuito descodificador que juntamos na Figura 20. É deste circuito que saem os sinais que são enviados à memória e que farão cumprir a função do comando representado pelo opcode descodificado.

Gráfico do descodificador dos opcode que determinam os comandos que o CM envia para a memória

Esses sinais são CKE, CS, RAS, CAS, WE, DQM, e AP. De 16 possíveis combinações destes sinais resultam no DIMM os 16 comandos referidos, como já veremos de seguida.

O CM ainda envia os sinais BA0 e BA1, que obtém do endereço que lhe é fornecido pela MMU. É ainda deste endereço que o CM obtém os parciais de linha e coluna que envia ao DIMM.

Resumindo, através do SPD o CM foi informado sobre as especificações do DIMM. Com base nesses elementos construiu a sua tabela de estados. Com base nessa tabela, vai enviando a um descodificador os opcode referentes aos comandos que, nos momentos próprios pretende executar na memória.

INICIALIZAÇÃO DA MEMÓRIA

Depois de completo o processo de identificação e após algum tempo de espera (cerca de 100 μs) com CLK e CKE em alta para permitir a estabilização da voltagem da alimentação à memória, o CM:

- executa uma Precarga a todos os Bancos.

- executa dois Auto Refresh seguidos

A execução deste processo tem por fim estabilizar os circuitos internos da memória que, ao ser ligado o computador se apresentam em estado indefinido.

Só então o CM executa o comando MRD (Definição de modo de registo),após o que está em condições de enviar ao DIMM os sinais resultantes da descodificação dos opcodes dos comandos.

Como ressalta do processo de inicialização, a precarga é o primeiro comando a ser executado na memória. A partir daí, cada comando de escrita ou leitura é sempre finalizado com um comando de precarga.

Daqui se depreende que as BL (Bit Line) estão sempre em carga, só sendo alterado esse estado durante uma operação de escrita ou leitura, mas logo seguidas da precarga.

Porquê esta observação?

Durante a análise do processo de leitura ou escrita na memória iniciámos sempre com a precarga, como não podia deixar de ser, porque as BL têm que estar carregadas e balanceadas para se poder proceder a uma leitura ou a uma escrita.

No entanto, nos quadros que elaborámos para os tempos, as operações de escrita ou leitura iniciam-se sempre por uma ativação de linha. Porquê? Precisamente porque a precarga já foi efetuada. Tal como descrito antes.

COMO SÃO RECEBIDOS OS SINAIS NO DIMM

A partir daqui já estamos do lado do DIMM. Todos os sinais enviados pelo CM são introduzidos na SDRAM por básculas sensíveis ao flanco ascendente do Clock. Portanto devem ser colocados pelo CM nos pinos dos Dies no ciclo anterior àquele em que a sua ação é pretendida.

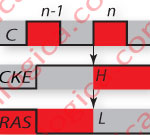

O sinal CKE valida ou não o sinal de clock sobre todos os comandos, conforme estiver em alta (1) ou em baixa (0). Ora, como o próprio CKE é introduzido na SDRAM no flanco ascendente de uma báscula, é necessário que CKE seja ativado no ciclo de clock anterior àquele em que se pretendem ativar os outros sinais.

Daí o facto de ser feita menção ao estado de CKE nos ciclos n-1 e n, isto é, no ciclo anterior àquele em que pretendemos ativar o comando e que é o ciclo n.

CKE

A Figura 25 representa o momento de mudança do valor dos sinais de CKE e RAS durante o ciclo de clock n-1, anterior àquele em que se pretende ativar RAS e o momento em que se ativam na memória, no ciclo n. Note-se que CKE é ativado no flanco ascendente do clock, estando em alta apenas depois dele. Portanto, nesse clock CKE não estará em alta no seu flanco ascendente. Ora, como as Básculas que introduzem os restantes sinais na memória são ativadas pela saída de uma porta AND cujas entradas são CKE e CLK, ambos devem estar em alta no flanco ascendente do clock em que se pretende introduzi-los. Confuso? Isto é lógica temporizada em pleno.

Agora é ao DIMM que compete interpretar os sinais que recebe e executar nos seus circuitos internos a função do comando que eles em

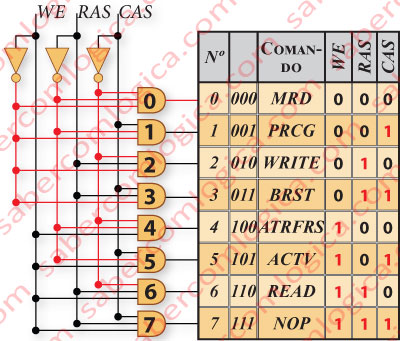

Gráfico do descodificador dos sinais WE. RAS e CAS em conjunto com a tabela da sua equivalência em comandos na memória.

conjunto pretendem fazer cumprir.

A combinação mais significativa dos sinais recebidos é representada pelos sinais WE, RAS e CAS, que só por si definem os 8 principais comandos, como se pode ver na Figura 21. Os restantes podem ser obtidos por combinação posterior com AP e DQM com exceção da entrada e a saída no modo de SLFRFR (Self Refresh), onde a variação de CKE vai ser a influente. É o único comando em que CKE vai assumir o valor 0, como veremos.

Construímos na Figura 21 um gráfico conjunto do MUX desmultiplicador das combinações desses 3 sinais ligado à tabela da representação dos comandos que ativam.

Vamos incluir este DEMUX na (7).

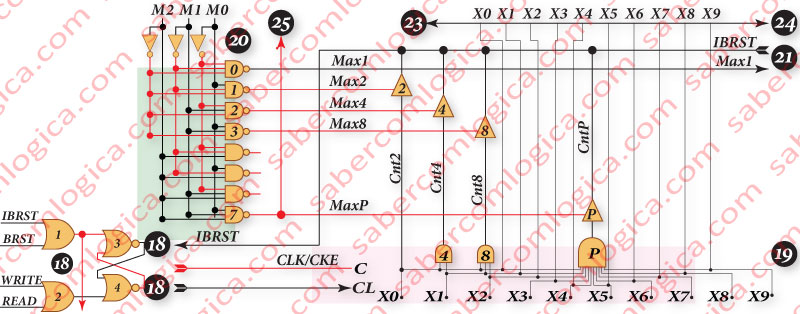

Os Registos a que nos vamos referir a partir de agora são constituídos por conjuntos de Básculas sensíveis ao flanco ascendente do clock.

O valor do endereço entra na memória pelos pinos A0 a A12 (2), que estão ligados às entradas do:

- Registador de Modo de Registo, (3),

- Registador de Endereço de Linha, (4)

- Registador de Endereço de Coluna,(5).

Os sinais CS e CKE são memorizados num registo acionado simplesmente pelo sinal de clock (8). O sinal CKE vai juntar-se com o sinal CLK (Clock) numa porta AND (9), que define o sinal de clock para toda a memória. É assim que o sinal CKE, enquanto se mantiver em baixa (0), consegue suspender a atividade da memória pelo número de ciclos de clock pretendidos.

Os sinais BA0, BA1, CAS, RAS, WE e DQM entram pelos respetivos pinos e ficam à entrada de um registo (6). Este registo é atuado só pelo sinal CLK (só CLK, sem CKE) assim passando para a sua saída. Os sinais WE, RAS e CAS são encaminhados para o DEMUX (7).

A função do sinal CS (Chip Select) é inibir o MUX descodificador dos sinais (7). Para isso está ligada a sua negação (¬CS) à entrada do MUX, de forma que quando CS está em alta, todas as saídas do DEMUX ficam em baixa, assim inibindo a emissão de comandos.

Relembramos que os comandos são ativos em alta (1). Por essa razão usámos a negação de CS (¬ CS).

Este DEMUX, ao tornar ativa uma saída de cada vez, garante-nos que em cada momento teremos um só comando ativo, em alta ou com o valor lógico 1, correspondente à tabela que, no quadro, fica junto do DEMUX. Os restantes comandos serão obtidos por combinações destes com outros sinais, como veremos adiante.

OS COMANDOS

MRD (MEMORY REGISTER DEFINITION)

Este é o último comando da inicialização da memória executada pelo CM. É através dele que são definidos alguns parâmetros que a memória vai utilizar durante a execução dos outros comandos que vai receber.

A combinação WE=0, RAS=0, CAS=0 (000) corresponde ao comando MRD. Com esta combinação dos valores daqueles sinais, este sinal estará ativo com o valor lógico 1.

Este valor será dirigido para o registador de MRD (3), onde em conjunto com o sinal CLK/CKE numa porta AND, ativa as básculas do registador, memorizando na sua saída os valores que se encontram à sua entrada.

Como é que esses valores são enviados pelo CM ao DIMM?

Quando o opcode 10 é escolhido pelo CM, gerando os sinais que ativam MRD, nos valores do endereço são colocados os parâmetros que se pretendem registar.

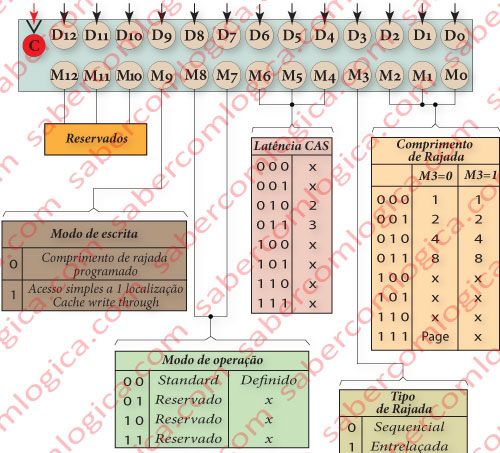

Significado dos bits do endereço quando está ativo MRD

Os parâmetros, conforme se pode acompanhar com a Figura 29 são:

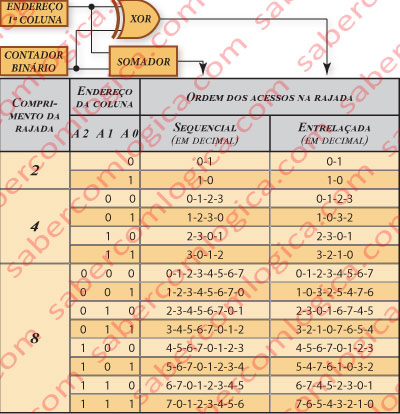

O COMPRIMENTO DA RAJADA, que pode ser de 1, 2, 4 ou 8 leituras, ou então de página inteira, o que corresponde à linha inteira, isto é, a 1.024 leituras. A leitura por rajada, tanto fixa como de página inteira deve ser sempre finalizada por um comando BRST, sob pena de a mesma continuar sempre de novo desde o início.

O TIPO DE RAJADA pode ser sequencial ou entrelaçado. Cada fabricante de processador usa o seu método de leitura, que o CM regista no

Como são definidos os tipos sequencial e entrelaçado da rajada e ao que correspondem nas diferentes dimensões de rajada

DIMM. Compete agora à memória, durante a execução da rajada fazê-lo de acordo com o parâmetro que foi definido. Para isso procede como descrito na Figura 28.

A rajada inicia-se na coluna definida pelo endereço. De seguida percorre todas as combinações dos bits

- A0, na rajada de 2,

- A0 e A1, na rajada de 4 e

- A0, A1 e A2 na rajada de 8,

de uma forma também pré-programada

- No método sequencial, os endereços de rajada obtém-se pela adição (23) do valor fornecido por um contador (19) ao endereço recebido do CM.

- No método entrelaçado, os endereços de rajada obtém-se pelo retorno de uma porta XOR (24) cujas entradas são os bits do endereço recebido do CM e o bits do contador binário (19),que parte de 0.

Em qualquer dos casos, todas as palavras na proximidade da selecionada são lidas. Numa rajada de 8, conseguem-se 8 leituras de 64 bits, ou seja, 64 bytes.

Na rajada de página, 1024 leituras são efetuadas. Neste caso não é possível o acesso entrelaçado. Esta rajada pode ser interrompida a qualquer momento pelo comando BRST.

A LATÊNCIA CAS (CL), como já vimos é o tempo de espera entre a ativação do sinal CAS e a estabilização dos sinais lidos das colunas selecionadas nos DQ dos DIMM. Tem um valor fixo em nanossegundos que é convertido em ciclos de clock conforme a frequência da memória.

O MODO DE ESCRITA pode ser definido entre a escrita por rajada, igual à leitura, ou a escrita em acessos pontuais, própria para quem opta pelo método de escrita write through cache.

Como veremos a seguir, na análise da cache, há dois métodos de escrita dos valores alterados em cache. Lá perceberão o sentido desta definição. Importa dizer que, tanto a leitura como a escrita na SDRAM estão concebidas em função do melhor aproveitamento da cache. Mas deixemos para lá o entendimento disto.

Portanto e a título de exemplo, se o CM enviar o endereço seguinte durante um comando de MRD

x x x 1 0 0 0 1 0 0 0 1 1

está a preparar a memória para trabalhar em modo de escrita por acessos individuais, para operar em modo standard, para uma latência CAS de 2 ciclos de clock, para rajadas do tipo sequencial e com o comprimento de 8.

Ficam assim estabelecidas as definições no Modo de Registo, até que novo comando MRD enviado pelo controlador volte a ativar as básculas do registador e os substitua por outros valores, ou seja cortada a alimentação elétrica.

ACTV (ATIVAÇÃO)

Este comando procede à ativação da linha de endereço, à ativação dos SA (Sense Amplifier) e à seleção do banco.

SELEÇÃO E ATIVAÇÃO DE LINHA

ACTV é ligado a uma porta AND em conjunto com o CLK/CKE. Quando ativo, ACTV é 1. Assim as básculas do registador do endereço de linha (4), quando CKE=1 e no clock seguinte, memorizam na saída o valor do endereço que se encontra na sua entrada, previamente enviado pelo CM, o endereço da linha.

Uma das ações que se pretende com este comando é a seleção de linha da matriz de acordo com o endereço enviado pelo CM. Portanto, há que fazer chegar á entrada do seletor de linha o valor deste endereço (10), o que é conseguido através da linha RAD (Row ADdress).

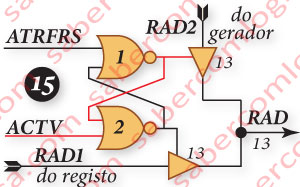

À ligação que representa os 13 bits do endereço de linha desde o registador até ao Seletor de linha, vamos chamar RAD1.

Mas há um outro comando que vai precisar de colocar também um endereço de linha na entrada do seletor, que é o ATRFRS. Só que esse endereço neste caso não é fornecido pelo CM mas por um contador interno (33), que analisaremos no âmbito desse comando. À ligação que representa os 13 bits do endereço de linha desde este circuito até ao Seletor de linha, vamos chamar RAD2.

Assim sendo, temos dois valores de endereço, provenientes de locais diferentes (RAD1 e RAD2) para comandos diferentes a ser colocados no mesmo local (RAD).

SELEÇÃO DA ORIGEM DO ENDEREÇO

Os dois endereços vão ser encaminhados para um seletor de endereço, na Figura 30 (15), que vai ter que escolher um dos dois, conforme o comando que estiver ativo seja ACTV ou ATRFRS.

O valor escolhido será o endereço de linha RAD que vai seguir para o Seletor de Linha.

Mas, os comandos ACTV e ATRFRS não têm que acontecer em sucessão um do outro. Portanto, enquanto não houver um comando ATRFRS será a linha do ACTV que fica na saída e vice-versa. O FFSR não muda de estado pelo facto da entrada que originou o seu estado mudar, mas porque a outra passa ao estado 1. Portanto, enquanto não acontecer um comando ATRFRS o endereço vindo do registador (4) vai permanecer na saída.

Mas este facto não terá qualquer influência no funcionamento do circuito. O que interessa não é se a linha selecionada se mantém na saída, mas se ela se mantém ativa na matriz depois do comando ACTV passar a 0.

Porque o que controla essa situação não se passa neste seletor de endereço, vamos seguir este sinal até ao Seletor de Linha da (10/12) onde podemos analisar a forma como este aspeto é controlado.

A seleção da linha será feita por uma estrutura em árvore de DEMUX que descreveremos em pormenor e em separado. A entrada desta estrutura será 1 quando pretendermos ter ativa a linha selecionada pelo endereço e será 0 quando não pretendermos ter nenhuma linha ativa, nem mesmo a selecionada.

Como dissemos e agora podemos verificar, o facto da linha permanecer selecionada não tem qualquer influência porque desta forma não estará ativa.

A linha de endereço tem que se manter ativa durante o tempo tRAS. Como ACTV é um comando de duração de 1 ciclo de clock, vamos usar um FFSR, na (12), ao qual o sinal ACTV faz o SET.

A precarga é efetuada com as linhas todas fechadas, inativas ou IDLE, sem o que o conteúdo de todas as células da linha ativa seria corrompido.

Portanto PRCG tem que colocar a matriz em IDLE. Será este o sinal que deverá fazer o RESET do FFSR.

Já temos os sinais ACTV e PRCG para funcionarem como SET e RESET do FFSR. Ligando a saída 1 deste FFSR ao primeiro DEMUX do seletor de linha obtemos o resultado pretendido.

Na Figura 32 veem-se várias linhas que podem funcionar como SET ou RESET do FFSR. Esses casos serão abordados junto com os respetivos comandos.

A análise em pormenor como os circuitos descritos funcionam para atingir o objetivo é descrita de seguida para que possa só ser lida por quem estiver interessado.

QUADRO 15

Representamos este quadro Figura 31 que colocamos aqui junto para o podermos analisar com mais pormenor com a descrição que segue.

Selector de endereços de linha para os comandos ACTV e ATRFRS…

O comando que dá origem a ACTV é enviado pelo CM num pulso de clock, passando logo de seguida a enviar comandos NOP. Mas ACTV e as suas ações têm que ser mantidos durante todo o tempo que a linha se mantiver ativa, tRAS, neste caso 5 ciclos de clock.

Estamos perante uma das tais situações referidas em que vamos utilizar um FFSR. Os bits de SET e RESET serão ACTV e ATRFRS.

Cada uma das saídas do FFSR fica ligada a um conjunto de 13 portas tristate ativas a 0, uma por cada linha de endereço proveniente da respetiva fonte.

Quando o comando ativo for ACTV dá-se um SET e a saída negada (porta NOR 2) fica a 0, ativando as correspondentes portas tristate, que permitirão a condução do endereço proveniente do registador de endereços de linha (4).

Quando o comando ativo for ATRFRS dá-se um RESET e a saída convencional (porta NOR 1) fica a 0, ativando as correspondentes portas tristate, que permitirão, a condução do endereço proveniente do contador (33).

E cada uma das saídas permanecerá no estado que cada um dos comandos lhe estabelecer até que o outro mude de estado.

Desta forma teremos sempre na linha RAD de junção das outras duas, a linha RAD correspondente ao comando ativo e só essa. Esta linha segue para o seletor de endereços.

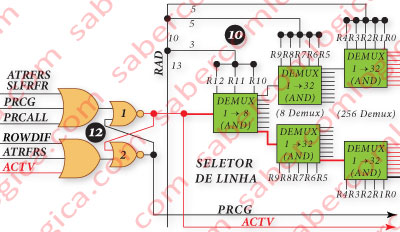

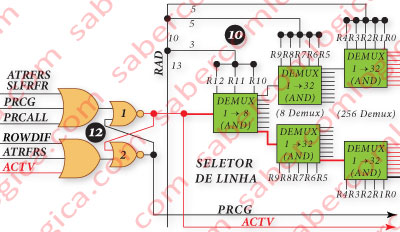

QUADRO 10

Este quadro é aqui representado pela Figura 32 junto com a sua descrição, por forma a permitir uma melhor análise.

O desmultiplicador (DEMUX) que seleciona a linha pelo endereço e executa o processo de manutenção do estado da linha em Ativo ou Idle.

Comecemos por falar no seletor de linha, que terá que selecionar uma de entre 8.192 linhas. Para este efeito imaginámos uma estrutura em árvore de DEMUX. Esta estrutura pretende só mostrar a lógica de seleção e ativação de uma linha.

Não será certamente a mais eficaz ou rentável, pois para os DIMM comerciais existem garantidamente algoritmos de grande complexidade que permitem soluções mais eficazes. Mas, como mais uma vez referimos, o objetivo deste trabalho é fazer entender a lógica de determinado procedimento e não encontrar a melhor solução.

Os DEMUX colocam uma entrada em tantas saídas quantas os bits de seleção permitem. Precisamente o contrário dos MUX, que permitem colocar numa saída tantas entradas quantas os bits de seleção permitirem.

Então, se colocarmos um determinado valor na entrada de um DEMUX, teremos esse valor refletido na saída que selecionarmos do DEMUX.

Se as portas de saída do DEMUX forem portas AND, a saída selecionada terá o estado lógico da entrada e todas as outras saídas terão o estado lógico 0.

Se as portas de saída do DEMUX forem portas NAND, a saída selecionada terá o estado lógico oposto ao da entrada e todas as outras saídas terão o estado lógico 1.

Com base nestas afirmações podemos dizer que, se colocarmos o valor 1 na entrada do seletor de linha e portanto na entrada do primeiro DEMUX (1 para 8 com portas AND) a saída selecionada pelos 3 bits de maior ordem do endereço (R12, R11 e R10) estará ativa a 1 e as restantes 7 saídas estarão a 0.

Ora, cada saída deste DEMUX constituirá a entrada de um outro DEMUX de entre 8. De todos eles, em cada situação só um terá a entrada a 1. Em cada um dos 8 DEMUX (de 1 para 32 com portas AND), haverá uma saída escolhida pelos seguintes 5 bits do endereço (R9, R8, R7, R6 e R5). Todas terão o valor igual ao da entrada de cada um. Portanto só um terá a saída a 1, aquele cuja entrada é 1.

Cada saída destes DEMUX vai agora ser a entrada de um novo DEMUX. Cada um destes 32×8=256 DEMUX (1 para 32 com portas NAND) terá uma saída selecionada pelos bits de seleção, os 5 bits de menor ordem do endereço (R4, R3, R2, R1 e R0) e terá uma entrada a 0, exceto aquele cuja entrada virá da saída selecionada do DEMUX que tinha entrada a 1.

Mas agora estes DEMUX têm portas de saída NAND, o que faz com que todos os que tenham entradas a 0 devolvam 1 em todas as portas e o que tem entrada a 1 devolva entrada 0 na porta selecionada e 1 nas restantes portas.

Resultado: 8.191 saídas a 1 e 1 saída ativa a 0.

Se na entrada do seletor colocarmos o valor 0, por identidade de raciocínio iremos encontrar 8.192 saídas a 1 no final.

Conclusão: Ao colocarmos o valor 1 ou 0 na entrada do Seletor de Linha, portanto do primeiro DEMUX, colocamos no estado ativo a 0 a linha selecionada se o valor for 1, ou todo o circuito em IDLE (ocioso), se o valor for 0.

Concluída aqui a descrição em pormenor dos quadros vamos prosseguir com a análise descritiva do circuito geral.

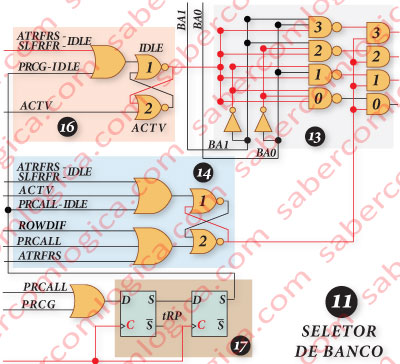

SELEÇÃO E ATIVAÇÃO DE BANCO

Todos os quadros intervenientes neste processo se encontram dentro do Seletor de Banco (11), que vamos analisar na totalidade, quadro a quadro com as suas interdependências, para melhor entender o que lá se passa e porquê.

Cada uma das linhas que sai do Seletor de Linha, liga a todos os bancos. Importa portanto selecionar e ativar um Banco ou todos, para que essa linha possa ser ativada nesse ou nesses Bancos.

Os sinais BA0 e BA1 do registador de sinais, são os bits de seleção do DEMUX de 1 para 4, com portas NAND, na (13). O valor da entrada é invertido na saída selecionada.

Como os bancos são ativos a 0, quando queremos um banco selecionado colocamos o valor 1 na entrada do DEMUX e na saída selecionada teremos o valor 0.

Se quisermos todos os bancos em estado ocioso (IDLE), colocamos o valor 0 na entrada do DEMUX. Assim a porta selecionada apresentará o valor 1.

Descrição em pormenor nos Quadros 16 e 17.

E, se em lugar de um Banco selecionado ou todos os Bancos ociosos, quisermos todos os Bancos selecionados?

Vamos ver. Cada uma das saídas do DEMUX vai agora entrar numa porta AND em conjunto com uma outra linha, que transporta um sinal que vai permitir:

- Validar todas as saídas do DEMUX se o seu valor for 1, pois neste caso a saída da porta AND assumirá o valor da outra entrada, ativando um Banco ou colocando-os todos no estado ocioso (IDLE), conforme aquilo que sair do DEMUX.

- Ativar todos os Bancos se o seu valor for 0, pois assim todas as portas AND terão as suas saídas a 0.

Com esta simples ligação encontrámos forma de, com a introdução de um valor 1 ou 0 em conjunto com cada saída do DEMUX em portas AND:

- Colocar todos os Bancos em IDLE.

- Selecionar e ativar um só Banco.

- Ativar todos os Bancos.

A questão agora coloca-se na forma como vamos encontrar e manter esses sinais durante o tempo de ativação dos bancos. Veremos na descrição do Quadro 14 como se consegue obter isto.

A análise em pormenor como os circuitos descritos funcionam para atingir o objetivo é descrita de seguida para que possa só ser lida por quem estiver interessado.

QUADRO 16

É através do circuito lógico deste quadro que se define o valor a colocar na entrada do DEMUX (13).

O Banco deve ficar ativo até que seja concluída a precarga, portanto pelo tempo de tRAS+tPR=tRC, que é o tempo mínimo entre dois sinais ACTV (7 ciclos de clock no nosso caso). Portanto a entrada do DEMUX tem que ficar a 1 durante todo esse período. Mas o comando ACTV só está ativo durante um ciclo de clock. Mais uma vez um FFSR será a solução.

O SET deste FFSR será efetuado pelo sinal ACTV, colocando a saída a 1 até que outros sinal faça o RESET.

A questão agora é saber qual o sinal que vai fazer o RESET. O que sabemos é que os bancos devem ficar todos ociosos (IDLE) no fim do ciclo, isto é, após decorrido tRAS+tRP. Sabemos também que isso se

dá no fim da precarga, ou seja, tRP ciclos depois do comando PRCG, no nosso caso 2 ciclos de clock após o comando PRCG.

Então e agora, como é?

Vamos ter que criar um contador de ciclos, ou atraso de ciclos, mais precisamente 2, na (17).

QUADRO 17

Para atrasar PRCG em tRP (2 ciclos de clock), vamos utilizar um conjunto de 2 Básculas D, em que

- o comando PRCG é ligado à entrada da 1ª

- a saída da 1ª está ligada à entrada da 2ª e

- a saída desta é ligada ao RESET do FFSR (16).

Assim, quando o comando PRCG é emitido o seu valor 1 fica na entrada da 1ª Báscula.

No clock seguinte (atraso de 1) esse valor passa à saída da 1ª e portanto à entrada da 2ª Báscula.

No 2º clock após a emissão de PRCG (atraso de 2), esse estado lógico passará à saída da 2ª báscula e portanto fará o RESET do FFSR (16) com 2 ciclos de atraso.

Aqui uma especial referência para a Lógica Temporizada e o seu entendimento.

- No clock seguinte à emissão do comando PRCG o seu valor já é 0, pois o CM emite um comando NOP. Certo?

- Dissemos bem, no clock seguinte, não no seu flanco ascendente, em que tanto PRCG passa a 0 nas saídas do Registador de Sinais, como o seu valor na entrada da 1ª Báscula (ainda a 1) passa à sua saída.

- Quando o novo valor de PRCG chega à entrada da 1ª Báscula já o anterior valor passou à sua saída, onde se mantém até ao clock seguinte.

- E assim sucessivamente. Lembramos que qualquer sinal registado na saída de uma Báscula permanece contínuo, mesmo com o clock em baixa.

Este reparo teve como intuito não só dissipar qualquer dúvida que se tenha levantado nos mais atentos, como salientar a importância da Lógica Temporizada em cada passo da atividade de um computador.

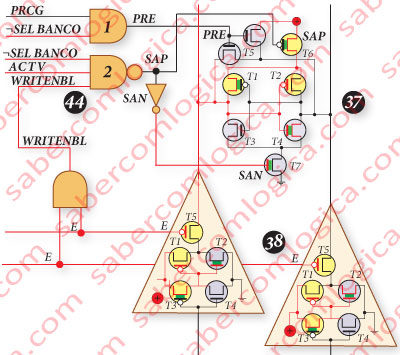

Conjunto 11 da Figura 30 onde se encontram os quadros 13, 14, 16 e 17

QUADRO 14

É o circuito lógico deste quadro que se vai definir o valor do sinal a introduzir nas portas AND que vão receber também as saídas do DEMUX (13).

Como este sinal faz para selecionar todos os Bancos já nós vimos aquando da análise do Quadro 13. O que queremos agora é saber como podemos manter o sinal ativo durante o tempo necessário. Mais uma vez vamos usar um FFSR para emissor desse sinal. A questão é, que comandos vão funcionar como SET e RESET.

O SET ao FFSR será feito por um comando PRCALL que, para efetuar a precarga a todos os bancos vai precisar de os ativar todos. Como a entrada da porta AND deve ser colocada a 0 para que todos os Bancos sejam ativados, então vamos retirar o sinal da saída negada do FFSR (porta 2).

O RESET será feito pelo comando ACTV, que assim garantirá que só será ativado o banco selecionado por BA0 e BA1.

Concluída aqui a descrição em pormenor dos quadros vamos prosseguir com a análise descritiva do circuito geral.

ATIVAÇÃO DOS SA (SENSE AMPLIFIER)

É este comando que vai ativar os SA (37). Para isso é necessário que SAP=0 (porta de um pMOS) e SAN=1 (porta de um nMOS).

É através do quadro (44) que são controlados os valores que a cada momento chegam a SAP, SAN e PRE. Vamos deixar mais para a frente, depois de se perceber como é que determinados sinais chegam a este quadro, a sua análise.

Para já importa reter que o valor contínuo ACTV(Sgn) já saído de um FFSR (12), aqui vai chegar e ativar os SA.

READ (LEITURA) E WRITE (ESCRITA)

O comando READ tem por fim colocar nos contactos DQ do DIMM os valores das células da linha e colunas selecionadas.

O comando WRITE tem por função, registar nas células da linha e colunas selecionadas, os valores provenientes dos DQ do DIMM.

A linha e o banco já se encontram selecionados e ativos, pelo comando ACTV.

No caso do comando READ o valor das células da linha aberta, já está sendo, amplificado, restaurado e colocado nos trincos pelo SA durante o tempo tRCD, aguardando só a abertura das PT (Portas Tristate) das colunas selecionadas para enviar o valor para os DQ, como já vimos anteriormente.

No caso do comando WRITE, o valor já se encontra à entrada dos BT (Buffer Tristate), aguardando só a sua abertura para seguir o processo de registo.

Vamos sempre lembrar que os comandos READ e WRITE são comandos que definem o início de rajada, pois a SDRAM foi concebida para acessos em rajada.

OS ENDEREÇOS DE COLUNA

São os comandos READ e WRITE que acionam a leitura dos endereços da coluna e sua colocação na saída do registo de endereços de coluna. Isto significa que antecipadamente, o CM colocou o endereço da coluna nos pinos de endereços.

Com este propósito:

- ligamos READ e WRITE a uma porta OR, onde qualquer um ativo (1) resulta numa saída ativa (1),

- saída essa que ligamos a uma porta AND junto com o sinal de CLK/CKE,

- que por sua vez estará ligada à entrada de clock do registador de endereço de colunas (5).

Assim, desde que um dos comandos READ ou WRITE esteja ativo, o sinal de clock chega ao registador de endereços de coluna, memorizando o valor do endereço nas suas saídas.

A DEFINIÇÃO DA RAJADA

INÍCIO DA RAJADA

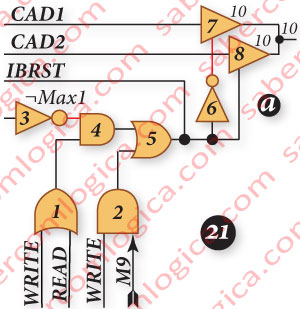

Para dar início à rajada, ligamos READ e WRITE a uma porta OR para termos uma saída ativa (1) desde que algum dos dois esteja ativo (1), ligando esta saída à entrada SET de um FFSR (18). Mais uma vez um FFSR, pois o sinal de pulso dado por READ ou WRITE tem de ser convertido num sinal contínuo enquanto a rajada durar.

Assim, quando qualquer um destes comandos estiver ativo (1) um SET é executado sobre o FFSR, cuja saída fica ativa (1) até que um sinal a 1 seja colocado na outra porta do FFSR, fazendo o seu RESET.

Serão os sinais BRST ou IBRST que ficarão ligados à outra entrada deste FFSR, funcionando assim como seu RESET e terminando a rajada.

EXECUÇÃO DA RAJADA

A rajada não é executada por, uma sucessão de comandos READ ou WRITE, mas por um contador interno (19). A Báscula deste contador tem uma entrada Cl (Clear), ativa a 0. Quando ativo, Cl executa um permanente RESET sobre o contador. Quando inativo Cl permite ao contador fazer o seu trabalho, executando a contagem.

Portanto, quando uma rajada estiver em execução Cl deve permanecer inativo pelo número de clocks igual ao comprimento da rajada. Da mesma forma deverá permanecer inativo enquanto uma rajada não estiver em execução.

Para conseguirmos este comportamento de Cl, precisamos de ter ligado a ele um sinal contínuo a 1 ou 0, conforme o caso. Mais uma vez a solução passa por um FFSR, na Figura 30 (18), sendo o seu SET executado pelos comandos READ e WRITE.

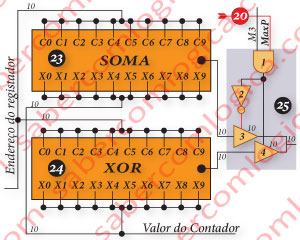

O tamanho da rajada foi definido pelo comando MRD e está guardado no registador de definições. Assim, os bits M0, M1 e M2 são ligados ao MUX que define o comprimento da rajada, na Figura 30 (20).

O bit M9=1 define o modo de escrita “Write Through Cache”, ou seja, escrita por acessos simples.

Vamos descrever passo a passo a interligação dos quadros intervenientes no processo de rajada.

SELEÇÃO DO ENDEREÇO

A linha CAD (Column Address – Endereço de coluna) chega ao seletor de endereços proveniente da Figura 30 (21). No circuito lógico deste quadro faz-se a seleção de uma entre duas linhas de endereço de coluna:

- Uma proveniente diretamente do Registador de Endereço de Colunas, CAD 1 e

- outra proveniente do circuito lógico da Figura 30 (23, 24, 25), designada por CAD 2.

Estas linhas serão selecionadas no quadro 21 (como se descreve na sua legenda), conforme se trate:

- de uma leitura ou escrita simples (rajada de 1), definida pela combinação 000 de M0, M1 e M2 ou pelo bit M9=1 que define “Write Through Cache”, caso em que o endereço CAD1 será a selecionado ou

- de uma leitura ou escrita em rajada, quando nenhuma das situações anteriores se verificar, caso em que o endereço CAD2 será a selecionado.

FORMAÇÃO DO ENDEREÇO

No caso de leituras ou escritas simples nada há que fazer ao endereço pois é selecionado diretamente do Registador.

Já no caso de leituras ou escritas em rajada o endereço tem que ser preparado.

A sua preparação consiste na construção dos endereços de rajada a partir do endereço inicial fornecido quando os comandos READ ou WRITE dão o sinal para o início da rajada.

O endereço vindo do Registador de endereços de Coluna está ligado a uma das entradas de dois circuitos:

- Um circuito somador, na Figura 30 (23)

- Um circuito lógico XOR, na Figura 30 (24)

à outra entrada destes dois circuitos está ligado o valor do contador de rajadas que origina, no circuito somador uma rajada sequencial e no circuito XOR uma rajada entrelaçada.

A saída destes 2 circuitos está ligada a um MUX (25), que vai selecionar um dos dois tipos de rajadas conforme o valor do bit M3 do Registador de definições for 1 ou 0 e verificar de que não se trata de uma rajada de página.

É deste circuito que é fornecido o endereço CAD2 que liga ao quadro 21.

O circuito onde é interpretado o comprimento de rajada, provocado o seu início e o seu termo e onde é feita a contagem dos ciclos correspondentes ao seu comprimento é o conjunto (18, 19 e 20).

No quadro 18 é onde se define o início e a terminação da rajada, pelo SET e RESET do FFSR, feito pelos sinais READ ou WRITE (SET) e BRST ou IBRST (RESET).

No quadro 19 encontra-se o contador, que inicia a contagem a 0 até ao comprimento da rajada menos 1. Cumprido esse valor tem de ser desencadeado o processo de terminação da rajada, sem o que o contador continuará reiniciando a contagem a 0 e assim sucessivamente.

O quadro 20 é um DEMUX (de 1 para 8) que tem como bits de seleção M0, M1 e M2, os bits do registador de definições onde está registado o comprimento de rajada.

É no conjunto destes dois quadros 19 e 20 que são produzidos sinais que vão permitir a execução da rajada de acordo com o definido. São eles:

- O sinal IBRST que vai para o quadro 18, onde termina a rajada.

- O sinal MaxP que informa o quadro 25 sobre se estamos ou não perante uma rajada de página conforme o seu valor seja 0 ou 1.

- O sinal Max1 que informa o quadro 21 se estamos numa leitura ou escrita isolada ou em rajada, conforme o seu valor seja 0 ou 1.

- Os valores da evolução do contador que vão para os quadros 23/24/25 onde são preparados os endereços para a execução da rajada

Mas este conjunto de é fundamentalmente um gestor do tempo de rajada, de forma a que possa emitir o sinal para a sua terminação no momento exato.

TERMINAÇÃO DA RAJADA

A rajada pode terminar:

- A qualquer momento por um comando BRST (BuRSt Terminate) enviado pelo CM,

- Após cumprido o seu comprimento e também por um comando BRST enviado pelo CM com a antecipação devida, tendo em conta os tempos que conhece,

- Ou porque simplesmente chegou ao fim nos casos de WRITEA e READA, por emissão de um comando interno.

Neste último caso o comando para a sua terminação tem que ser gerado nos circuitos internos do DIMM, acompanhando a evolução do contador de rajadas (19) e tendo presente o seu comprimento, já determinado nas saídas do DEMUX (20).

Vamos dar-lhe o nome de IBRST.

O sinal introduzido na linha que conduz IBRST vai até ao FFSR (18) onde faz o seu RESET ativando o sinal Cl do contador. A linha IBRST liga também aos quadros 28/40/41/42/43/47 onde é feito o tratamento interno das latências.

A análise em pormenor como os circuitos descritos funcionam para atingir o objetivo é descrita de seguida para que possa só ser lida por quem estiver interessado.

QUADROS 23/24/25

Descrito no texto sob o título Quadros 23, 24 e 25

O valor das saídas do contador está ligado a um circuito SOMA (23) e a um circuito XOR (24), como 1º operando. O endereço vindo do registador de colunas é o 2º operando dos 2 circuitos. Da SOMA sai uma rajada sequencial e do XOR uma rajada entrelaçada.

A seleção do circuito a adotar é feita pelo bit M3. Como a escolha entrelaçada não é possível na rajada de página, o bit M3 é ligado em conjunto com o estado da saída 7 (111) do DEMUX (20), transportado na linha MaxP, à porta AND1.

A saída desta porta está ligada ao MUX de 2 para 1 (25), que seleciona os endereços próprios do tipo de rajada escolhido.

Conforme a saída de AND1 for 1 ou 0 assim as portas Tristate 3 ou 4 (10 portas em cada para as 10 linhas de bit de cada endereço) estarão ativas selecionando respetivamente a rajada sequencial (AND1=1) ou a rajada entrelaçada (AND1=0).

QUADRO 21

Representação local do quadro 21 da Figura 30

Este quadro está descrito na Figura 36 onde se faz a seleção entre as linhas de endereço CAD1 (direto do Registador) e CAD2 (dos Quadros 23, 24 e 25).

As portas Tristate 7 (10 portas para 10 linhas de bit) permitem ou não a passagem de CAD1. As portas Tristate 8 permitem ou não a passagem de CAD2.

A saída da porta OR5 define através do MUX (21a) qual das portas Tristate 7 ou 8 é ativa (0), portanto qual dos endereços CAD1 ou CAD2 é selecionado. OR5 será 1 se AND2=1 ou OR1=1. Se a saída de OR5 for 1, CAD1 será selecionada. Se OR5 for 0, CAD2 será selecionada.

AND2 será 1 se estivermos perante um comando WRITE e M9 estiver definido a 1.

AND1 será 1 se estivermos perante comandos READ ou WRITE e se Max1 for 0, isto é, se uma rajada de 1 estiver definida por M0=0,M1=0 e M2=0.

Em ambos estes casos o endereço CAD1 será selecionado. Em casos diferentes o endereço CAD2 será selecionado.

QUADROS 18/19/20

As saídas significativas do DEMUX 19, com exceção da saída 0, estão ligadas a portas Tristate (2, 4, 8, P) através das linhas Max2, Max4, Max8 e MaxP, que serão ativas a 0 conforme os bits M0/M1/M2 definirem rajadas de 2, 4, 8 ou Página, respetivamente.

Cada uma destas portas Tristate está a intercetar uma linha que vem do contador de rajadas (19). São essas linhas Cnt2, Cnt4, Cnt8 e CntP, que analisam os valores de X0 diretamente e de X0/X1, X0/X1/X2 e X0 a X9, combinados através das portas AND4, AND8 e ANDP respetivamente.

Zona de interligação dos quadros que intervêm na formação da rajada

Relembrando que a primeira posição do contador é 0, a que corresponde a primeira Leitura/Escrita no endereço definido pelo Registador, quando X0 ou as portas AND referidas devolverem o valor 1 é porque as linhas analisadas estão todas a 1, isto é, o contador chegou à 4ª ou à 8ª rajada ou Página (tudo a 1).

Como a porta Tristate referente ao comprimento de rajada pretendido está ativa, quando o seu valor for atingido (X0=1 ou AND?=1), na linha IBRST será introduzido o valor 1 através da correspondente linha Cnt?

No caso de rajada de 1 definida pela linha Max1, a linha IBRST está diretamente ligada à saída da porta OR5 do seletor (21), que assume o valor 1 (¬Max1) quando Max1 é 0 (1ª rajada).

Desta forma está garantido que IBRST ficará a 1 quando algum dos tamanhos predefinidos de rajada for atingido.

O valor IBRST segue para a entrada de RESET do FFSR do quadro 18, colocando a sua saída a 0 e portanto o valor de Cl a 0, ou seja ativo. IBRST passa de imediato a 0 e o contador fica em permanente RESET.

Concluída aqui a descrição em pormenor dos quadros vamos prosseguir com a análise descritiva do circuito geral.

SELEÇÃO DE COLUNA

Selecionado o tipo de rajada, o endereço encontrado é ligado ao seletor de colunas (26). O princípio de funcionamento do seletor de colunas é o mesmo do seletor de linha, pelo que nos dispensamos de fazer nova descrição. Basta ler a já feita para o seletor de linhas.

Tal como nesse, a entrada para a estrutura de DEMUX define o valor das saídas. Se a entrada tiver o valor lógico 1, as colunas selecionadas pelos bits do endereço estarão ativas. Se a entrada para a estrutura de DEMUX tiver o valor lógico 0, todas as colunas estarão inativas.

Pretende-se que o sinal gerado pelo comando se prolongue pelo tempo CL (CAS Latency). Também aqui vamos ter um FFSR (27) a definir a entrada da estrutura de DEMUX.

O SET do FFSR será feito por qualquer um dos comandos READ ou WRITE, através de uma porta OR a que ambos são ligados (27).

O RESET do FFSR (27) será feito pelo comando PRCG que colocará o seletor de colunas em IDLE, isto é, sem nada selecionado.

ATIVAÇÃO DE COLUNA

Como vimos atrás, os valores de entrada na SDRAM passam através de um BT (Buffer Tristate). Quando ativos, durante um comando WRITE e selecionados pelas condições devidas, estes vão forçar os valores da sua entrada nas BL (Bit Line) e nas células da linha ativa por ela servidas.

Por sua vez, os valores a serem lidos na célula de memória, vão sê-lo através de um SA (Sense Amplifier) que ,depois de os sentir, os vai amplificar, restaurar nas células e colocar em trincos de saída. O SA funciona com duas BL (Bit Line) por cada coluna, uma que serve as linhas par e outra que serve as linhas impar. A saída dos valores selecionados será determinada pela ativação da PT (porta tristate).

Assim, vamos ter que informar a ativação sobre várias condicionantes:”Se a linha é par ou impar e se se trata de uma escrita ou de uma leitura”.

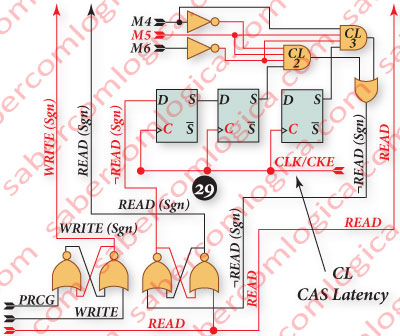

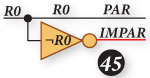

Representação do quadro 29 da Figura 30

Estes valores são formados nos quadros (29) e (45) e são aqui colocados junto nas Figuras 40 e 41.

A informação READ e WRITE é levada por duas linhas, uma para cada, que vão chegar às portas OR onde os BT e as PT são ou não ativados.

Pretende-se manter os sinais de READ e WRITE no seu estado até ao final da rajada, isto é, até ao ciclo de clock seguinte ao da última rajada. Como estes comandos têm a duração de um ciclo de clock, mais uma vez vamos ter de recorrer a dois FFSR, um para cada linha

Como nesse ciclo é ativado o comando PRCG, será este que vai funcionar como RESET de ambos os FFSR. O SET de cada FFSR será efetuado por cada um dos comandos READ ou WRITE.

Na Figura 40 nota (29) já devem ter reparado em algo diferente do habitual. A saída utilizada nos FFSR não é a sua saída convencional mas a sua saída negada.

Na realidade, quando WRITE ou READ forem comandos ativos, o seu valor será 1 e provocarão um SET do FFSR que ficará com a respetiva

Quadro onde é formada a informação sobre linha par ou ímpar.

saída a 1. Mas, o que nós pretendemos é que o sinal levado até às portas de seleção seja ativo a 0. Por isso escolhemos a saída negada dos FFSR.

A determinação da informação sobre se a linha é par ou impar também vai ser levada às portas de seleção por duas linhas saídas do quadro (45), também aqui representado na Figura 41.

O valor que nos permite determinar se uma linha é par ou impar é o do bit R0. Se R0=0 é par, se R0=1 é impar.

Basta ligar R0 diretamente à linha que vai servir as portas que ativam as BL de linhas pares e ligar a sua negação a outra linha que vai servir as portas que ativam as BL das linhas impares.

Portas de selecção de colunas

Ficamos assim com todos os sinais que necessitamos para ativar o BT que vai servir o propósito desejado no local desejado, assinalados na Figura 42.

Mas falta ainda fazer com que os valores que os SA leram nas células da linha ativa sejam memorizados nos trincos. Isso consegue-se através do comando READ, que irá funcionar como sinal de clock nos trincos (46), representado aqui pela Figura 43.

Mas este sinal tem que ser aplicado ao banco ativo e à linha par ou impar, conforme a selecionada. Mais ainda. Neste caso o que queremos é mesmo o comando READ, o tal de um ciclo de clock e não o sinal READ(Sgn).

Então vamos ter que levar o valor do comando READ até ao quadro de controlo do clock dos trincos de memorização das leituras dos SA, onde vai ser combinado com o valor de SELBANK e de LINHA PAR ou LINHA IMPAR.

Mas o comando READ é ativo a 1 e todos os outros são ativos a 0. Então vamos negar o comando, ¬READ e levá-lo nesse

Quadro de clock dos trincos

estado até às portas onde vai ser analisado em conjunto com eles.

Como o sinal de clock deverá obviamente estar a 1, a porta que fará a análise deverá devolver 1 quando todas as condições forem 0. Será uma porta NOR.

E cá temos o nosso clock para os trincos de memorização dos valores lidos pelos SA.

A ALIMENTAÇÃO DO SA (SENSE AMPLIFIER)

Os SA devem manter-se alimentados durante o período decorrido após o comando ACTV, até ao início da precarga, isto é pelo tempo tRAS, período em que vão sentir, ler e restaurar os valores nas células da linha ativa.

É este restauro que pode demorar para além da conclusão das leituras a fazer e que vai obrigar a respeitar sempre o tempo tRAS como mínimo para ter os SA alimentados.

Durante uma escrita, os SA também sentem, leem e restauram os valores das células que não são escritas.

Aliás, se a fase de restauro não se completasse, muitos valores poderiam ficar comprometidos. E o restauro prolonga-se para além do comando WRITE.

Nas células a escrever, portanto nas colunas selecionadas por WRITE, tal restauro não é necessário, pois vai ser garantido pelo BT (Buffer Tristate).

No entanto, nestas colunas os SA têm que ser desligados, como já vimos atrás na análise de acesso à célula da memória, sob pena de interferirem no processo de escrita e destruírem a informação.

Após este período que vai até à ultima leitura ou escrita da rajada e no mínimo a tRAS, inicia-se o processo de precarga, situação em que a sua alimentação deve estar garantida pela alimentação através dos transístores PRE, mantendo para isso as suas portas a 1.

A análise em pormenor como os circuitos descritos funcionam para atingir o objetivo é descrita de seguida para que possa só ser lida por quem estiver interessado.

Com todos estes requisitos vamos lá ver como é que se resolve a questão, analisando a Figura 44.

Quadro de comando do SA

O SA está alimentado quando a porta do transístor T6 está a 0 (pMOS). Interessa-nos portanto, para que o SA esteja em carga, obter uma resposta a 0 do conjunto de condições que conduzem a esse facto.

Quando o comando ACTV é emitido é selecionado um banco e, para o banco selecionado, os SA passam a ser alimentados. Se ligarmos a uma porta NAND os sinais de ACTV(Sgn) (Ativo=1) e da negação ¬SELBANK (¬Ativo=1), enquanto estes sinais tiverem o estado lógico 1 a resposta de NAND é 0 e o SA estará em carga.

Mas os SA da coluna selecionada, em caso de escrita têm que ser desligados. Certo?

A seleção da coluna é feita por um sinal de Enable que vai ligar aos BT de entrada fechando o seu transístor T5. E o sinal de Enable é ativo a 0. Por cada SA temos dois BT, um para cada BL (Bit Line), um que serve linhas pares e outro linhas impares.

Então, o que temos que fazer é verificar se algum dos BT está selecionado. Se assim for, uma das linhas de Enable terá o estado 0. Se WRITE não for o comando em causa ou se a coluna em causa não for selecionada, ambas as linhas de Enable terão o estado 1.

Conclusão: “Ligamos estas duas linhas a uma porta AND e vamos chamar à sua saída WRITENBL (Write Enabled- Escrita selecionada). Depois ligamos esta saída à mesma porta NAND onde já tínhamos ACTV e ¬SELBANK”.

Se WRITENBL for 1, então NAND devolve 0 e os SA ficam ativos. Se WRITENBL for 0, caso em que há uma escrita em curso nessa coluna, a porta NAND devolve 1 e o SA desliga-se.

Agora, só temos que fazer chegar este valor à porta do transístor T6 do SA, tendo assim cumprida a condição em que ele se deve manter alimentado. Da linha que vai a T6 (SAP) fazemos derivar uma outra que passa por uma porta NOT invertendo o seu valor, ligando-a à porta do transístor nMOS T7 (SAN), que passará a ligar o circuito à terra.

Outra condição para que o SA possa estar alimentado é não estar em decurso uma precarga.

Ora, o comando PRCG desativa o comando ACTV e portanto a condição anterior deixa de se verificar. A porta NAND, passando a ter uma entrada falsa (ACTV=0), devolve 1.

Estando em decurso uma precarga, as portas dos transístores T5 (PRE) têm que estar a 1.

Nesse sentido colocam-se na entrada de uma porta AND o sinal de PRCG(Sgn) e de ¬SELBANK. Se ambos forem 1 a saída dessa porta será 1 e os transístores PRE terão as suas portas a 1.

Ficam assim cumpridos os requisitos de alimentação de um SA para os diversos comandos da SDRAM.

Concluída aqui a descrição em pormenor dos quadros vamos prosseguir com a análise descritiva do circuito geral

READA, WRITEA E PRCG

READA E WRITEA

READA e WRITEA são sinais idênticos a READ e WRITE, com uma única diferença:

- No caso de READ e WRITE é o CM que envia um comando PRCG no momento próprio que calcula de acordo com as latências que lhe são fornecidas para a memória em questão.

- No caso de READA e WRITEA deverá o comando PRCG ser executado automaticamente por decisão tomada pelos circuitos internos da memória no momento próprio, que calcula de acordo com os valores do Registador de Definições.

Para um melhor entendimento do comando PRCG, vamos incluir no diagrama do circuito interno os circuitos necessários ao cálculo do seu ponto de emissão.

A determinação do momento certo para introduzir o comando PRCG depende da análise das latências, que têm que ser respeitados na evolução dos comandos executados sobre a SDRAM.

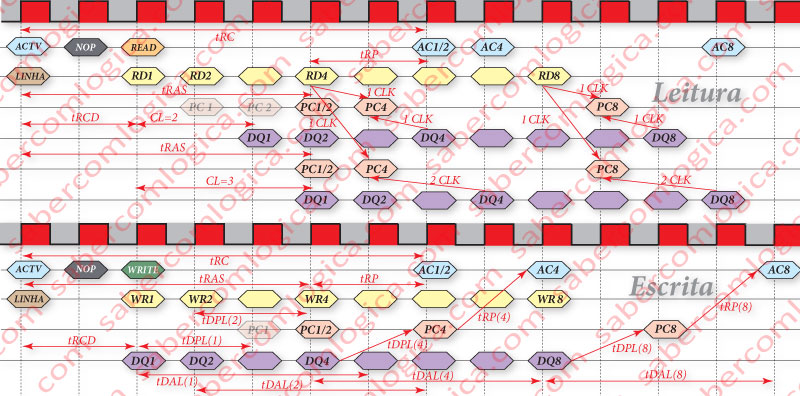

ANÁLISE DAS LATÊNCIAS

Vamos acompanhar com a Figura 45, onde tentámos fazer transparecer tudo o que dissemos algumas páginas atrás sobre latências, do ponto de vista da relação entre eventos dentro do circuito da SDRAM.

Tempos a respeitar entre as diversas operações sobre a SDRAM, quer em READ que em WRITE

No circuito geral esta análise é feita nos quadros da Figura 30 (28/39/49/41/42/43/47). Para o objetivo pretendido todos estes quadros estão interligados, recebendo sinais uns dos outros. Repare-se inclusive que o primeiro a intervir no processo (28) vai ser desativado pelo sinal de PRCG emitido pelo último (30). Por isso, como vem sendo hábito, vamos fazer uma primeira descrição sintética e sem pormenores do que se vai passar globalmente e depois faremos uma análise para cada quadro de como se consegue cada um dos objetivos que vamos enunciar.

Antes de mais vamos relembrar quais são os tempos a respeitar para a emissão de um comando PRCG e vamos tentar relacioná-los com algo que seja possível detetar dentro do circuito.

Uma condição que desde já sabemos ter que ser respeitada é que tRAS tem que estar esgotado antes da emissão de um comando PRCG. Para determinarmos quando tal acontece, vamos utilizar o contador (43) que é ativado pelo comando ACTV. Quando tRAS se cumprir um valor a que vamos chamar RAS será emitido a partir de (43) para se instalar numa entrada de (42), onde vai assinalar a sua chegada através de uma presença contínua, como RAS(Sgn).

E porquê contínua?

Porque como já sabemos, a emissão do comando PRCG efetua-se sempre depois de cumprido tRAS, o que é assinalado por RAS(Sgn) no estado 1, mas sempre depois de:

- Durante um comando READA:

- 1 ciclo de clock antes do último dado a ler quando CL (CAS Latency) for 2.

- 2 ciclos de clock antes do último dado a ler quando CL (CAS Latency) for 3.

- Durante um comando WRITEA:

- depois de cumprido o tempo tDPL após a última leitura da rajada feita aos DQs.

Assim sendo, tRAS tem que permanecer ativo e contínuo para podermos verificar quando todas as condições se cumprem, o que é feito no quadro 42.

Como acabámos de verificar os tempos de espera para emissão de um comando PRCG diferem conforme estejamos num comando READA ou num comando WRITEA. Por isso cada uma das situações vai ser analisada em quadros separados, concretamente no quadro 40 para o comando READ e no quadro 41 para o comando WRITE, que enviam sinais para o quadro 42 onde a decisão final é tomada.

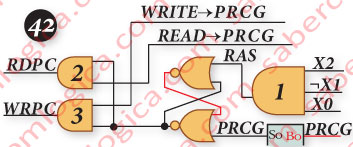

Estamos agora em condições de saber quando emitir o comando PRCG, o que vai ser decidido no quadro 30.

PRCG

A EMISSÃO DO COMANDO

Quadro onde é feita a interpretação dos valores das latências e obtidos os valores de saída que vão entrar nos locais correspondentes do quadro na Figura 41

Portanto no quadro 42 estão os sinais que representam o cumprimento das diferentes latências que condicionam a emissão de um comando PRCG.

Quando a latência de um comando READ ou WRITE se esgota é comparada com tRAS e quando qualquer uma delas junto com tRAS se verificarem são emitidos os sinais RDPC e WRPC conforme se dê para um comando READ ou WRITE.

Os sinais agora emitidos são transportados para o quadro 30, onde a informação sobre as várias condições que condiciona a emissão de um comando PRCG se juntam:

- RDPC informando quando pode ser emitido um comando de Auto Precarga após o fim de uma rajada de leitura gerada por um comando READ.

- WRPC informando quando pode ser emitido um comando de Auto Precarga após o fim de uma rajada de escrita gerada por um comando WRITE.

- PRCG, vindo diretamente do CM, quando é este que ordena uma Precarga.

Quando alguma destas situações se verifique, assumindo o valor 1, é emitido um comando de Precarga ou Auto Precarga que agora se confundem, sendo colocados na mesma linha.

A forma como esta decisão é tomada em pormenor poderemos ver na descrição do quadro 30 mais à frente.

O QUE FAZ

O desmultiplicador (DEMUX) que seleciona a linha pelo endereço e executa o processo de manutenção do estado da linha em Ativo ou Idle.

Um comando PRCG pressupõe a existência de um Banco selecionado, ao qual ele se dirige. É pressuposto um comando PRCG é emitido após um comando ACTV.

O comando PRCG vai fechar a linha aberta por ACTV, atuando como RESET no FFSR do quadro Figura 30 (12), aqui reproduzido pela Figura 32. Como já sabíamos, durante a precarga as células da matriz não podem estar acessíveis, sob pena de ser destruído o seu conteúdo.

No entanto, o banco selecionado vai-se manter ativo para que a sua precarga possa ser efetuada. Mas só durante o tempo que durar a precarga, pois quando esta terminar todos os bancos têm que ficar no estado ocioso (IDLE).

Então, temos que saber quando termina a precarga. Para isso o sinal PRCG é introduzido na entrada da 1ª báscula de um conjunto de 2 (17), que têm por fim a contagem de tRP (2 clocks) e o atraso do fecho dos bancos nesse tempo, o tempo para execução da precarga.

Sendo a saída da 2ª báscula ligada ao RESET dos quadros (16) e (14), quando o sinal PRCG lá chegar vai colocar todos os bancos em IDLE e vai fazer com que o FFSR (14) deixe de forçar a seleção der todos os bancos, se for o caso (será em PRCALL).

Para que se efetue a precarga, o sinal PRCG, este já contínuo pois vem do FFSR (12) é levado a uma porta AND onde é analisado conjuntamente com o banco ativo (44), aqui reproduzido pela repetição da Figura 44. Se ambos forem verdade abrem os transístores T5 (PRE) do SA, iniciando a precarga do banco selecionado enquanto ele o estiver, durante tRP.

A análise em pormenor como os circuitos descritos funcionam para atingir o objetivo é descrita de seguida para que possa só ser lida por quem estiver interessado.

DESCRIÇÃO DOS QUADROS 28/43

Por que o que pretendemos é ter um sinal contínuo, concretamente ACTV(Sgn), mais uma vez vamos usar um FFSR. Neste caso o comando ACTV faz o seu SET e o comando PRCG o seu RESET.

A saída do FFSR está ligada à entrada Cl (Clear) do contador. Assim com Cl=0 o contador estará em permanente RESET e com Cl=1 inicia e prossegue a contagem.

Portanto após a emissão de um comando ACTV o contador inicia uma contagem que interrompe após a emissão do comando PRCG.

Os valores de X0, ¬X1 e X2 da saída do contador são avaliados pela porta AND1 que, quando X0=1, ¬X1=1 e X2=1, tendo portanto na contagem o valor tRAS=5 (101), devolve 1. Este sinal a 1 será aquele a que chamamos RAS e vai ser uma das entradas do quadro 42, indicando que a partir daquele ciclo está cumprido o tempo tRAS.

Mas outros parâmetros vão ter que ser verificados para poder autorizar a emissão de um comando PRCG, inclusivamente diferentes no caso de um comando READ e mesmo entre um comando READ e um comando WRITE. Por isso, antes de prosseguirmos com mais quadros vamos analisar a Figura 45 para entendermos depois a análise dos quadros em que tal avaliação será feita.

DESCRIÇÃO DA FIGURA 45

Na parte superior do gráfico analisamos o caso de um comando READ que origina uma rajada de 8 leituras. Foram consideradas ambas as situações de CL (CAS Latency) poder ser de 2 ou 3 ciclos de clock.

Na parte inferior do gráfico analisamos o caso de um comando WRITE que origina uma rajada de 8 escritas.

Em qualquer dos casos o que se pretende evidenciar é a relação entre os pontos de emissão de comandos PRCG , a presença de dados nos DQs e a emissão de novos comandos ACTV.

NO CASO DE READA

RD1, RD2, RD4 e RD8 representam os ciclos de clock em que é efetuada a última leitura durante uma rajada de 1, 2, 4 e 8, respetivamente.

DQ1, DQ2, DQ4 e DQ8 representam os ciclos de clock em que os dados vão estar presentes nos DQs no final das rajadas de 1, 2, 4 e 8, respetivamente, para poderem ser lidos.

PC1, PC2, PC4 e PC8 representam os ciclos de clock em que o comando PRCG podem ser emitidos em situações de rajadas de 1, 2, 4 e 8, respetivamente. PC1/2 representa o ciclo de clock de emissão de um comando PRCG nos casos em que tanto o ciclo de emissão de PC1 como o de PC2 foram ultrapassados ou se juntam no de PC2, por motivo de se ter que cumprir o tempo tRAS.

AC1/2, AC4 e AC8 representam os ciclos de clock em que um novo comando ACTV pode ser emitido.

As setas a vermelho indicam os tempos a respeitar entre os diversos comandos. As inclinadas têm indicação do número de clocks entre os eventos pelas mesmas indicados.

Podemos neste gráfico verificar que, para qualquer dos dois valores de CL (2 ou 3), existe um comportamento padrão comum:

“O comando PRCG é efetuado no ciclo a seguir à última leitura da rajada, mas nunca antes de tRAS estar cumprido”.

Como tal, PC1 e PC2, que representam os comandos PRCG para rajadas de 1 e 2 vão acontecer depois de tal ser possível, precisamente porque tRAS ainda não se tinha esgotado. Já PC3 e PC4 começam após a última leitura das respetivas rajadas.

Portanto, conforme o comprimento da rajada duas situações diferentes se podem verificar na escolha do tempo a utilizar para o cumprimento dos requisitos.

NO CASO DE WRITEA

WR1, WR2, WR4 e WR8 assinalam os ciclos de clock em que é efetuada a última leitura de dados dos DQs e se inicia o respetivo processo de escrita nas células.

DQ1, DQ2, DQ4 e DQ8, PC1, PC1/2, PC2, PC4 e PC8 e AC1, AC2, AC4 e AC8 têm o memo significado que anteriormente.

As setas a vermelho indicam os tempos a respeitar entre os diferentes comandos. As setas com indicação de tDPL(1), tDPL(2), tDPL(4 )e tDPL(8) indicam os tempos a respeitar entre a última leitura dos DQs na rajada indicada entre parênteses e a consolidação do seu registo nas células. As linhas indicadas com tRP(1), tRP(2), tRP(4) e tRP(8) indicam os tempos a respeitar entre a emissão do último comando PRCG para cada uma das rajadas indicadas entre parênteses e a emissão de um novo comando ACTV.

Como se pode verificar no gráfico, no caso do comando WRITE o início da precarga só se pode dar tDPL depois da última leitura dos DQ, o que acontece nos ciclos de clock indicados por WR1, WR2, WR4 e WR8.

Portanto para um comando WRITE a escolha dos tempos é completamente diferente da utilizada para a escolha efetuada para o comando READ.

DESCRIÇÃO DOS QUADROS 40/41

É nestes quadros que vai ser determinado quando pode ser emitido o comando PRCG em função do comprimento da rajada e do facto de estarmos em presença de um comando WRITEA ou de um comando READA.

O fim da rajada é anunciado pelo comando IBRST. Lembramos que este é o comando de terminação de rajada gerado internamente ao circuito, precisamente para ser usado com os comandos READA e WRITEA, casos em que o CM não emite o comando BRST nem o comando PRCG.

NO CASO DE READA

Como vimos na análise à FIGURA 45, no caso de um comando READA o comando PRCG pode ser emitido no ciclo de clock seguinte à última leitura efetuada pela rajada.

O comando interno IBRST assume o valor 1 quando é executada a última rajada. Pode portanto a linha que o transporta provocar a emissão de um comando PRCG no ciclo de clock seguinte.

Como temos que o atrasar um ciclo, colocamos IBRST na entrada de uma báscula (40), cuja saída vai refletir esse valor no ciclo de clock seguinte, portanto com um clock de atraso.

É este procedimento que tem equivalência com a colocação do comando PRCG pelo CM na saída do registo de entrada de sinais no ciclo seguinte ao do fim da rajada.

E assim encontramos o sinal READ→PRCG, a “autorização para passar do modo READ para o modo PRCG”, sinal este que vai entrar na avaliação feita no quadro 42.

NO CASO DE WRITEA

Tal como na leitura, a linha IBRST é ligada à entrada do conjunto de 2 Básculas do quadro 41, que vai provocar um atraso de 2 ciclos de clock no seu sinal para que quando o sinal de fim de rajada chegar ao quadro 42 se tenha esgotado tDPL que tem o valor de 2 clocks.

E assim encontramos o valor WRITE→PRCG, a “autorização para passar do modo WRITE para o modo PRCG”, sinal este que vai entrar na avaliação feita no quadro 42.

DESCRIÇÃO DOS QUADROS 42/47

É neste quadro, aqui junto descrito pela Figura 47, que se vai decidir qual dos valores de latência vai influenciar a emissão do comando PRCG.

Quadro onde é tomada a decisão sobre quando emitir um comando PRCG, de acordo com o facto de estamos ou não em READA ou WRITEA, o que é indicado por AP.

Os valores conseguidos pela determinação do cumprimento dos tempos de latência entre a última leitura e a última escrita de uma rajada e PRCG, READ→PRCG e WRITE→PRCG vão agora constituir cada um uma entrada de uma das duas portas AND2 e AND3 respetivamente, sendo a outra entrada dessas duas portas o sinal RAS conseguido da determinação do cumprimento do tempo tRAS.

Se tRAS já se esgotou, essa entrada das 2 portas AND vai estar a 1, pelo que, quando o valor de IBRST atrasado também for 1 como pretendido, uma das portas vai devolver o valor lógico 1, conforme for READ ou WRITE.

Foi por essa razão que convertemos tRAS de um pulso de clock num sinal contínuo que vai ficar à espera que os outros cheguem para fazer a avaliação.

Se tRAS não se esgotou então serão os valores atrasados de IBRST que vão ficar à espera que tRAS se cumpra.

Mas esperem!

IBRST também é um sinal de um só ciclo, como verificámos atrás. Mais um caso em que um pulso tem que ser convertido num sinal contínuo por um FFSR.

Vai ser com o FFSR (47) antes da entrada das básculas (40) e (41). O SET do FFSR (47) será feito pelo pulso de IBRST que assim será convertido num sinal contínuo IBRST(Sgn) até que outro pulso atue no RESET do FFSR (47). Como o resultado desta análise vai lançar um comando PRCG, vamos ligar esse sinal ao RESET do FFSR (47), ocasião em que a linha IBRST(Sgn) passará a conduzir o valor 0.

Agora sim! Qualquer um dos sinais que vai chegar às portas AND2 e AND3 do quadro 42 vai manter o seu estado 1 até que o seu parceiro dessa porta assuma também esse estado.

Cada uma das linhas que sai de cada uma das portas AND do quadro 42, RDPC da porta AND2 ou WRPC da porta AND3, irá ter o valor 1 conforme seja o caso de um comando READA ou WRITEA, quando for o momento correto para emitir um comando PRCG.

DESCRIÇÃO DO QUADRO 30

Estes sinais vão ligar ao quadro 30, onde é decidida a emissão do comando PRCG, quer na sequência de comandos READA e WRITEA quer dando seguimento a um comando PRCG vindo do CM. Juntamos a representação isolada desse quadro na Figura 47.

Neste quadro avaliam-se duas situações distintas:

- Se foi enviado um comando PRCG pelo CM e o valor de AP é 0.

- Se estivermos num comando READ ou WRITE e AP for 1, é porque se trata de um comando com auto precarga. Quando os valores de RDPC ou WRPC chegarem ao quadro 30, são convertidos em READA e WRITEA, lançando então o sinal de PRCG.

Este é o princípio básico da avaliação. Mas não é assim tão elementar como isso. Para podermos fazer a avaliação do ponto 2, precisamos de saber se estamos perante um comando READ ou WRITE quando algum dos sinais RDPC ou WRPC chegar a este quadro.

Os comandos são sinais instantâneos e vão ter que ser comparados com os sinais RDPC e WRPC, que só vão chegar 1 ou 2 ciclos após o fim da rajada (IBRST). E vão chegar ambos, pois a sua emissão é efetiva após IBRST.

Para sabermos qual dos dois nos interessa, isto é, se estamos perante um comando READ ou WRITE, ambos vão ter que deixar a sua marca.

E então como é que eles marcam a sua emissão?

Novamente com um FFSR. Um para cada comando, precisamente para que possamos sempre saber qual o comando que está em curso.

Se o comando em curso é READ, então

- A entrada da porta AND3 proveniente do FFSR 6/7 fica a 1 depois de o comando READ fazer o seu SET.

- Se se tratar de um comando READA, então AP também está a 1.

- Ficam estes dois a aguardar até que chegue à 3ª entrada da porta AND3 o comando RDPC proveniente do quadro 42, também com o valor 1.

- Com as 3 entradas a 1, o comando READ converte-se num comando READA e emite um comando PRCG para o seu circuito próprio.

Se o comando em curso é WRITE:

- A entrada da porta AND2 proveniente do FFSR 4/5 fica a 1 depois de o comando WRITE fazer o SET desse FFSR.

- Se se tratar de um comando WRITEA, então AP também está a 1.

- Ficam estes dois a aguardar até que chegue à 3ª entrada da porta AND2 o comando WRPC proveniente do quadro 42, também com o valor 1.

- Com as 3 entradas a 1, o comando WRITE converte-se num comando WRITEA e emite um comando PRCG para o seu circuito próprio.

Se o comando em curso é PRCG, para que seja mesmo este comando que o CM quer enviar e não um PRCALL, AP deverá ser 0. Ligados a negação ¬AP e PRCG à porta AND1, segue um comando PRCG para a porta OR onde se junta com READA e WRITEA. Se algum destes tiver o valor 1, OR terá o valor 1. Teremos então uma precarga ou uma auto precarga, que a partir deste momento são iguais.

Embora o sinal proveniente dos FFSR seja contínuo, o sinal PRCG saído da porta OR vai durar apenas um ciclo de clock pois:

- No caso da porta AND1, o comando PRCG vem do CM, portanto com 1 ciclo de clock de duração.

- No caso das portas AND2 e AND3, a sua saída vai ficar a 0 no ciclo de clock logo a seguir, pois tanto RDPC como WRPC também vão passar a 0.

Repare-se que é o próprio sinal PRCG que vai fazer o RESET do FFSR do quadro 42 no clock seguinte àquele em que é emitido.

Daí a existência de uma Báscula nesse quadro, pois é necessário parar a evolução do comando no ciclo em que é emitido e produzir o seu efeito no ciclo seguinte.

Uma chamada de atenção para a afirmação que fizemos de que as Básculas eram assim como as estalagens onde os estafetas eram obrigados a parar e descansar ao fim do dia, para prosseguirem o seu trabalho no dia seguinte.

Já tentaram perceber o que iria acontecer se essa Báscula não existisse?

Pois o sinal agora com o valor 1 do comando PRCG iria fazer o RESET do FFSR e por influência de WRPC ou RDPC fazer-se passar a si próprio ao valor 0 ainda durante o mesmo ciclo de clock, chegando ao fim do clock com o valor 0 ou indefinido. E era este valor que iria contar.

Mais uma para a Lógica Temporizada.

Concluída aqui a descrição em pormenor dos quadros vamos prosseguir com a análise descritiva do circuito geral

PRCALL

Este comando tem que ser tratado de uma forma separada do comando PRCG, pois ativa situações diferentes.

Assim, quando é recebido o comando PRCG, o seu sinal é comparado com AP (22) numa porta AND.

Se ambos estiverem no estado lógico 1 é porque se trata de um comando PRCALL. Então a saída dessa porta AND, que assume o estado lógico 1, passa a ser a condutora do comando PRCALL. Nesta situação o comando PRCG não é ativado, pois no quadro (30) a sua combinação com o valor de AP na porta AND1 resulta em 0.

Ora, como para ser lançado um comando de Precarga, o seletor de linhas tem de estar em IDLE, o sinal PRCALL deve também ser ligado à entrada SET do FFSR (12), colocando o seletor de linhas em IDLE e lançando o sinal contínuo PRCG(Sgn) que vai ligar os transístores PRE (44).

PRCALL vai também atuar sobre a entrada SET do FFSR (14) do seletor de banco, o que resulta na seleção de todas as linhas do seletor de bancos, ou seja, na ativação de todos os bancos, como já vimos na análise do quadro (11).

De seguida liga-se o sinal PRCALL ao conjunto de básculas (17), lançando assim a contagem de tRP, tempo ao fim do qual ele se encontra na saída da 2ª báscula.

Esta última ligação é feita pelos dois sinais PRCG e PRCALL, ambos ligados a uma porta OR que por sua vez vai ligar ao quadro (17).

Ligando esta saída à entrada RESET do FDFSR (14), voltamos a selecionar o banco definido pelo MUX (13) do seletor de bancos. Ligando também essa saída ao RESET do FFSR (16), colocamos o seletor de bancos também em IDLE.

Fica assim cumprida a função de PRCALL. Os bancos estão todos precarregados e o sistema está em IDLE.

BRST

BRST (Burst Terminate) ou Término de Rajada é um comando usado para terminar uma rajada de leitura ou escrita a qualquer momento. Terminate é mesmo para terminar. Já não pode recomeçar.

Para interromper uma rajada utilizar-se-ia o CKE, colocando no seu valor lógico a 0 durante o número de ciclos de clock em que se pretende interromper a rajada, reiniciando-se a mesma a partir do ponto onde foi interrompida quando se repusesse o valor lógico de CKE a 1.

Para terminar a rajada, liga-se o sinal BRST ao RESET do FFSR (18), seguindo-se todo o processo já descrito para IBRST.

Só que, contrariamente a IBRST, no caso de BRST não existe qualquer auto precarga, pelo que após um sinal de BRST o CM tem que enviar sempre de seguida um sinal de PRCG.

Não vamos apresentar gráficos separados para os comandos que seguem, pois a dispersão dos quadros envolvidos tal dificulta. Por isso o acompanhamento deve ser feito com o próprio diagrama, que vem já de seguida.

ATRFRS

(Auto Refresh) ou refrescamento automático é uma operação que tem que ser efetuada pelo menos uma vez em cada 64 ms a todas as 8.192 linhas em cada Banco. Pode em alternativa ser efetuada a uma linha de cada vez em cada 7,8 ms, ou 7800 ns, ou ainda a cada 780 ciclos de clock. ATRFRS é executado em simultâneo em todos os Bancos.

Antes de enviar um comando de ATRFRS, o CM envia sempre um comando de PRCALL, exceto se o comando de ATRFRS vier na sequência de um anterior, pois o comando ATRFRS termina com PRCALL.

A contagem e a periodicidade dos comandos de ATRFRS são da responsabilidade do CM. A memória limita-se a executar o comando que lhe é enviado e as funções que lhe são inerentes, respeitando os tempos definidos.

O comando ATRFRS não é um comando persistente, isto é, corresponde a um pulso e dá-se uma vez. Por cada operação de ATRFRS a uma linha, o CM deve enviar um comando, controlando a sua periodicidade e quantidade. Portanto o CM pode enviar:

- 8.192 comandos ATRFRS seguidos espaçados de tRC (7 ciclos de clock), iniciando esta rajada a cada 64 ms.

- 1 comando ATRFRS por cada 780 ciclos de clock

O CM não envia qualquer endereço para este comando, pois o mesmo é gerado dentro da memória num contador de refrescamento (33), que vai sempre incrementando o valor do endereço e que fica sempre na última linha a ser refrescada. Como já sabemos os contadores são rotativos, por isso, ao chegar a 8.191 (213-1) volta ao início (0).

Veremos já de seguida qual a lógica que permite a execução de um comando ATRFRS.

SLFRFR

Quando, depois de ativado o comando ATRFRS, o sinal CKE passa ao estado lógico 0, a memória passa ao modo SLFRFR. A lógica que provoca a entrada e a saída em SLFRFR está no quadro (36).

O processo de SLFRFR é um processo completamente autónomo da memória, usado por exemplo quando os sistemas são colocados em Stand By, preservando os valores em memória, para tal as suas células tendo que ser refrescadas.

Neste caso o CM (Controlador de Memória) desliga-se, ficando o DIMM completamente entregue a si próprio. Como o sinal de clock deixa de lhe ser fornecido, o DIMM vai gerar o seu próprio sinal de clock, pois agora não precisa de estar sincronizado com nada. O CM e todo o restante sistema estão a dormir.

Veremos já de seguida qual a lógica associada ao modo SLFRFR.

A análise em pormenor como os circuitos descritos funcionam para atingir o objetivo é descrita de seguida para que possa só ser lida por quem estiver interessado.

DESCRIÇÃO DA LÓGICA DE ATRFRS

O comando ATRFRS enviado pelo CM é colocado numa linha que se vai ligar :

- Ao RESET do FFSR (15), colocando a sua saída no valor lógico 0 e ativando as portas tristate que vão deixar passar o endereço vindo do gerador de endereços (33) para os processos de Auto Refresh e Self Refresh da memória.

- Ao SET do FFSR (12) onde vai fazer a ativação da linha correspondente ao endereço escolhido.

- Ao SET do FFSR (14) onde ativa todos os bancos.

Com os bancos todos ativos, a linha que transporta o ACTV(Sgn) de (12) para (44) vai forçar a alimentação dos SA de todos os bancos, que entretanto se encontram precarregados pelo comando PRCALL.

Ativada a alimentação dos SA, estes vão sentir, ler e restaurar o valor das células da linha selecionada.

E o tempo que têm para fazer este trabalho é tRAS.

E como é que o circuito sabe o que é tRAS ?

O sinal ATRFRS vai ligar à primeira báscula de um conjunto de 7 Básculas (32) que vai gerir os 7 ciclos de clock correspondentes a tRC, entre dois ACTV.

Quando ATRFRS é 1, este seu valor vai chegar à 5ª báscula ao 5 clocks, indicando assim que se esgotou tRAS, o tempo mínimo entre ACTV e PRCG. A saída dessa 5ª báscula é ligada à entrada RESET do FFSR (12). Desta forma, quando tRAS se esgota o seletor de linhas é colocado em IDLE.

Um ciclo de precarga é iniciado através da linha que transporta PRCG(Sgn) para o quadro 44. Neste caso será um comando de PRCALL, uma vez que os Bancos estão todos ativos, resultado da ação que o comando ATRFRS teve sobre o FFSR (14).

Ao fim de 7 ciclos de clock, cumprido o tRP, que é o tempo da Precarga até uma ativação ou colocação do sistema em IDLE, a saída da última báscula de (32) assume o valor lógico 1.

Esta saída final das 7 básculas está ligada:

- À entrada do sinal de clock do contador gerador de endereços (33) provocando assim o incremento do endereço, que fica preparado para novo comando ATRFRS.

- À entrada RESET do FFSR (14), onde anulará a seleção de todos os bancos.

- À entrada RESET do FFSR (16) onde colocará todos os bancos em IDLE.

DESCRIÇÃO DA LÓGICA DE SLFRFR