Registos de deslocamento

Por vezes é necessário deslocar os bits de um Registo para a esquerda ou para a direita.

Concretamente nas operações de multiplicação e divisão em que baixamos e chegamos à esquerda ou baixamos e chegamos à direita, este é o procedimento.

Deslocar um bit de um número à esquerda equivale a multiplica-lo por dois. Deslocar um bit de um número à direita equivale a dividi-lo por dois

Uma utilização frequente destes circuitos é a conversão de transmissões em paralelo (um barramento completo, p.e 8 bits) para transmissões em série (1 bit de cada vez). São colocados os 8 bits nas saídas do Registo de Deslocamento e inicia-se um conjunto de 8 deslocações. Por cada deslocação sai um bit para a linha de transmissão em série. No final volta-se a colocar nas saídas do Registador de Deslocamento o valor a converter e reinicia-se o processo.

Idêntico tipo de descrição vale para a conversão inversa.

Por cada deslocamento à esquerda sai um bit à esquerda e entra um bit novo à direita. Cada bit passa a ocupar o lugar do que fica imediatamente a seguir e à sua esquerda.

Por cada deslocamento à direita sai um bit à direita e entra um bit novo à esquerda. Cada bit passa a ocupar o lugar do que fica imediatamente a seguir e à sua direita. Se não houver um bit específico definido para entrar em cada deslocamento entra por defeito um bit novo com o valor 0.

O Registo de Deslocamento é constituído por um conjunto de Básculas, tantas quantos os bits de largura dos Registadores da CPU, ligadas sequencialmente entre si, isto é, as entradas de umas provêm da saída de outras.

E porquê registos de básculas e ligados entre si?

Como dissemos, cada bit vai ocupar a posição doutro à esquerda ou à direita. Por isso as Básculas serão ligadas entre si da forma que veremos para cada tipo deslocamento. Mas sempre a saída de uma à entrada da seguinte.

A Báscula garante-nos que qualquer valor que chegue à sua entrada após o erguer do Clock só será memorizado no próximo erguer do Clock. Após cada deslocamento temos de congelar o grupo de bits deslocado e processá-lo. E para que isto seja possível, como já vimos na Lógica Temporizada, vamos ter que usar Básculas.

Mais uma vez é evidente a função da Lógica Temporizada em qualquer operação. Aqui é responsável pela sincronização dos deslocamentos com o clock. Um deslocamento por cada Ciclo de Clock.

O termo Memorizar que temos usado, refere-se ao registo de valores das entradas das Básculas nas suas saídas.

Rotação de Bits à Direita

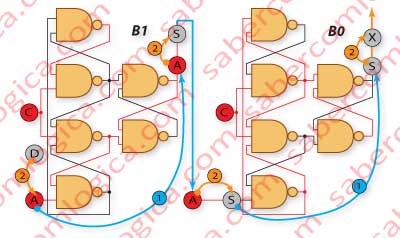

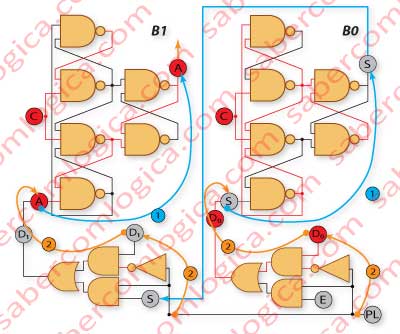

Na Figura 1 representamos um Registo de Deslocamento à Direita de 2 bits. B1 é a Báscula do bit de ordem 1 e B0 é a Báscula do bit de ordem 0

- Preparado para entrar em B1 está o bit D.

- A saída da B1 está ligada à entrada da B0 (B1→B0).

- Na saída da B0 está o bit X que vai sair do Circuito.

- A e S estão nas entradas de B1 e B0.

Quando o clock sobe :

- A e S passam às saídas de B1 e B0, o que é representado pelas linhas a azul claro com o número 1.

- A passa para a entrada da B0 pela ligação B1→B0 e D está agora na entrada da B1, o que é representado pelas linhas a laranja com o número 2 .

- Nas saídas de B1B0 a composição S X passou a A S.

- No clock seguinte (não mostramos a representação):

- D e A passam às saídas de B1 e B0 – linhas a azul

- B sai fora pela oseta a laranja.

- TNas saidas de B1B0 a composição A,S passou a D,A.

A evolução global em B1B0 foi (esquerda→direita):

DA→SX D→AS→X DA→SX

Rotação de Bits à Esquerda

Na Figura 2 representamos um Registo de Deslocamento à Esquerda de 2 bits, com as Básculas B1 e B0.

- O bit a entrar D, no circuito está na entrada da B0.

- O bit a sair X está na saída da B1..

- A saída de B0 está ligada à entrada de B1 (B0→B1).

Referimos aquilo que é diferente do circuito do Registo anterior. No restante vale a descrição anterior, no sentido inverso. No entanto é interessante que tentem efetuá-la e cheguem à conclusão certa.

A evolução B1B0 que tivemos foi (esquerda←direita):

XA←SD X←AS←D XA←SD

In the global evolution showed for both the circuits, the shaded letters mean:

- Rosa – Bits para entrar

- Azul – Bits que saíram

- Amarelo – Bits nas saídas das Básculas..

Verificação de Deslocamento

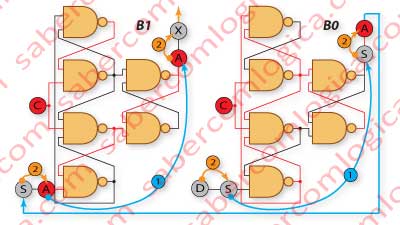

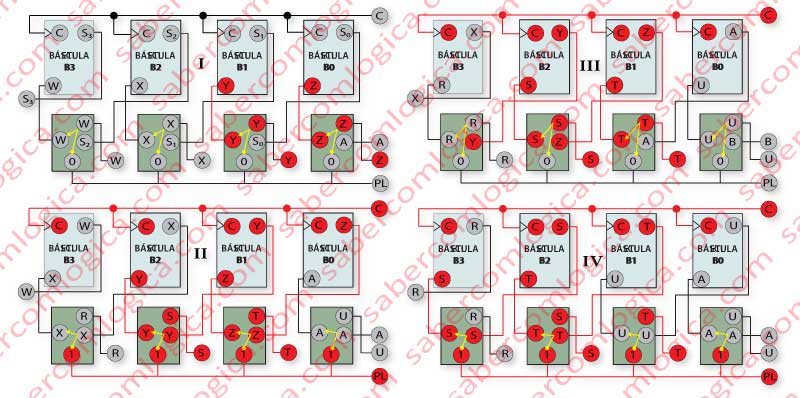

Vamos fazer a análise do comportamento de dois Registos de Deslocamento de 4 bits em representação reduzida ao longo de vários Clocks, na Figura 3.

Note-se que os bits libertados do Deslocamento à esquerda nos Quadros I a V são os que entram na Deslocamento à direita dos Quadros VI a X e vice versa. Formamos assim um circuito fechado, isto é, duas deslocações sequenciais à esquerda e à direita.

As setas azuis representam as ligações entre Básculas e o seu sentido.

As setas laranja representam a entrada e a saída do circuito e o seu sentido.

As setas violeta tracejadas representam a passagem dos valores das entradas→saídas de cada Báscula no flanco ascendente do Clock.

Deslocamento à Esquerda

Quadro I– Apresenta a situação inicial do Registo de Deslocamento à Esquerda com o Clock em baixa. W,X,Y,Z em B3,B2,B1,B0 são os bits a deslocar

- Na entrada da B0 está o bit A, o que entra.

- As ligações são B0→B1,B1→B2,B2→B3.

- B3 liberta o bit W.

Quadro II – 1º Clock.

- W é libertado por B3 para o Quadro VII.

- A entra no registo em B0 libertado do Quadro VII.

- Os valores de B3,B2,B1,B0 passam a X,Y,Z,A.

Quadro III – 2º Clock.

- X é libertado por B3 para o Quadro VIII.

- B entra no registo em B0 libertado do Quadro VIII.

- Os valores de B3,B2,B1,B0 passam a Y,Z,A,B.

Quadro IV – 3º Clock.

- Y é libertado por B3 para o Quadro IX.

- D entra no registo em B0 libertado do Quadro IX.

- Os valores de B3,B2,B1,B0 passam a Z,A,B,D.

Quadro V – 4º Clock.

- Z é libertado por B3 para o Quadro X.

- E entra no registo em B0 libertado do Quadro X.

- Os valores de B3,B2,B1,B0 passam a A,B,D,E.

Deslocamento à Direita.

Quadro VI – Apresenta a situação inicial com Clock em baixa. E,D,B,A em B3,B2,B1,B0 são os bits a deslocar.

- Na entrada da B3 está o bit W, o que entra.

- As ligações S/E são B3→B2,B2→B1,B1→B0

- A saída da B0 liberta o bit A.

Quadro VII – 1º Clock

- A é libertado por B0 para o Quadro II.

- W entra no registo em B3 libertado do Quadro II.

- Os valores de B3,B2,B1,B0 passam a W,E,D,B.

Quadro VIII – 2º Clock.

- B é libertado por B0 para o Quadro III.

- X entra no registo em B3 libertado do Quadro III.

- Os valores de B3,B2,B1,B0 passam a X,W,E,D.

Quadro IX – 3º Clock.

- D é libertado por B0 para o Quadro IV.

- Y entra no registo em B3 libertado do Quadro IV.

- Os valores de B3,B2,B1,B0 passam a Y,X,W,E.

Quadro X – 4º Clock.

- E é libertado por B0 para o Quadro V.

- Z entra no registo em B3 libertado do Quadro V.

- Os valores de B3,B2,B1,B0 passam a Z,Y,X,W.

Um detalhe nos resultados finais a ser evidenciado.

No quadro X está ZYXW, o número invertido de WXYZ, que entrou no quadro I.

No quadro V está ABDE, o número invertido de EDBA, que entrou no quadro II.

Conclusão: Dois deslocamentos à esquerda e à direita em sequência invertem os bits de um número, neste caso em concreto B3→B0, B2→B1, B1→B2, B0→B3.

Registos de deslocamento com carregamento em paralelo (PL)

Quando falámos na utilização destes circuitos para conversão de transmissões em paralelo para série, dissemos a determinado momento que: “coloca-se lá outro conjunto de 8 e começa-se desde o princípio”.

Quem é que lá os põe e como é que o faz? Certamente não somos nós a colocar um por um os novos bits no Registo?

De operações como esta que utilizam estes circuitos ressalta a necessidade de prever a possibilidade de carrega o Registo de Deslocamento em determinado momento com um novo número a deslocar.

Então, o que nós queremos é um circuito que possa efetuar dois tipos de operações: Deslocar e Carregar.

E é para isso que existem os Registos de Deslocamento com Carregamento em Paralelo (PL).

Antes da entrada de cada Báscula do Registo de Deslocamento vamos ter um porteiro, que a cada operação (ciclo de clock) pergunta o que se pretende fazer. E depois manda executar a operação pretendida, isto é, ele executa uma operação condicionada pela resposta à pergunta, uma operação condicional.

E então qual é a pergunta que ele faz?

Quer continuar a deslocar? E nós respondemos:“Sim, é verdade, 1” ou “Não, é falso, 0”. E cá temos nós uma resposta humana convertida em binária a escolher uma de entre duas possibilidades.

Quem fazia uma coisa assim parecida era o Multiplexer, nosso velho amigo de há tempos. Pois é, e é precisamente um MUX que vai estar antes da entrada de cada Báscula.

E como ele tem que escolher entre Deslocar e Carregar, vamos colocar nas suas entradas:

O bit da saída da Báscula ligada a esta, para quando a escolha for Deslocar.

O bit do número a carregar com a mesma ordem desta Báscula, para quando a escolha for Carregar.

E para ele se decidir informamo-lo com um bit chamado PL (Paralel Load – Carga em Paralelo), se Desloca com PL=1 (“Sim, é verdade, continua a deslocar”), ou se Carrega com PL=0 (“Não, é falso, não continua a deslocar”). Este é o bit de seleção do MUX de 2 para 1.

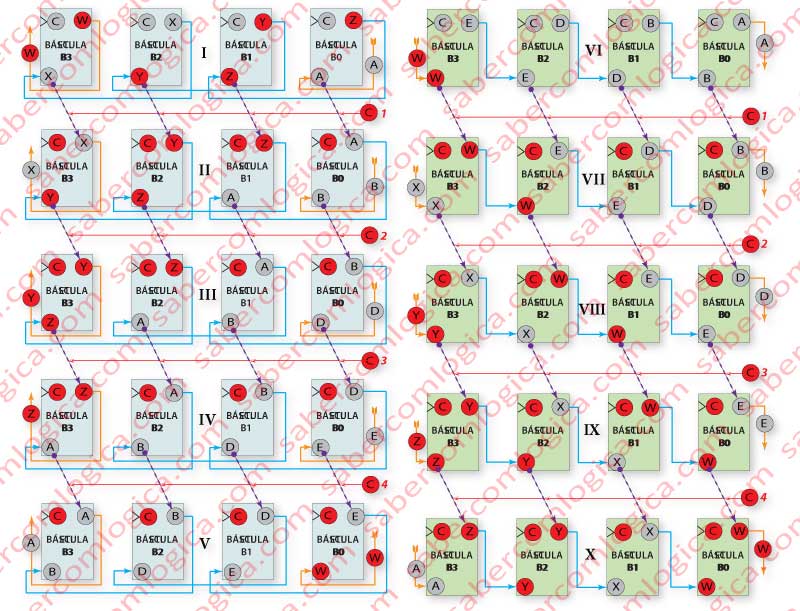

Na Figura 4 está representado um Registo de Deslocamento à esquerda com PL que faz o deslocamento e na Figura 5 um Registo de Deslocamento à esquerda com PL que faz o carregamento, ambos com 2 bits.

Vamos designar estes Registos por Registo de Deslocamento com PL (com Carregamento em Paralelo).

No caso dos gráficos destas figuras tal com na definição anterior PL foi definido como ativo a 0, isto é, o MUX executa uma carga em paralelo quando PL=0.

Mas não tem que ser obrigatoriamente assim, dependendo essa definição da forma como as variáveis a selecionar forem ligadas ao MUX. Isso sim condiciona o estado de ativo de PL em cada caso.

Na Figura 5, scomo PL é 0, está selecionado o carregamento dos dados D0 e D1. .

As linhas a azul claro indicam a memorização das entradas (entradas→saídas) em B1 e B0.

As linhas larajas indicam as entradas D0 e D1 selecionadas nos MUX pelo sinal de seleção PL, que ficam na entrada de cada Báscula preparadas para entrar no circuito no próximo ciclo de clock.

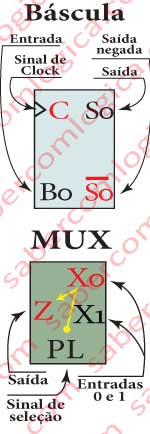

A Figura 6 legenda a representação gráfica reduzida das básculas e dos multiplexer usados nos quadros exemplificativos de movimento de bits da Figura 7. As linhas a amarelo representadas no multiplexer simbolizam qual das entradas X0 ou X1, está a ser colocada na saída Z pelo sinal de controlo PL.

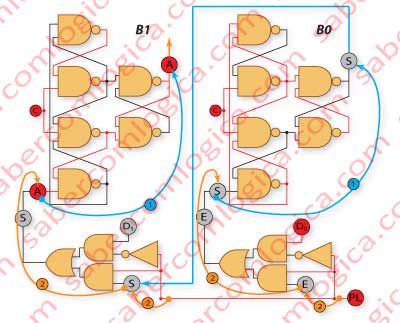

Na Figura 7, podem-se visualizar as ligações referidas. Representa-se um Registo de Deslocamento à esquerda com PL. Vamos acompanhar uma situação de carregamento, seguida de um deslocamento e de outro carregamento. O objetivo é poder visualizar como evoluem no MUX e na Báscula as diversas ligações que ativam as diferentes possibilidades.

Na entrada 1 dos MUX são colocados os valores a deslocar (selecionados por PL=1

Na entrada 0 dos MUX são colocados os valores a carregar (selecionados por PL=0)

Quadro I – uação inicial com o clock em baixa. O número W,X,Y,Z is at the MUX entra0,está na entrada 0 dos MUX preparado para ser carregado no Registo por PL. Como PL é 0 é esta a entrada selecionada pelo que os bits deste numero são colocados nas entradas de B3,B2,B1,B0.

Quadro II – 1º Clock.Os valoress W,X,Y,Z nas entradas das Básculas são memorizados. É assim efetuado o carregamento em paralelo. Nas saídas de B3,B2,B1,B0 ficam os valores W,X,Y,Z.

Os bits X,Y,Z estão na entrada 1 dos MUX de B3,B2,B1. Na entrada 1 do MUX de B0 está A, o bit que entra.

Embora na entrada 0 dos MUX esteja já um novo número R,S,T,U a carregar, são os bits do deslocamento X,Y,Z,A que vão ficar nas entradas de B3,B2,B1,B0, pois PL é 1 e seleciona a entrada 1 dos MUX.

Quadro III – 2º Clock. Os valores X,Y,Z,A nas entradas das Básculas são memorizados. É assim efetuado o deslocamento à esquerda dos bits de W,X,Y,Z que ficam agora com os valores X,Y,Z,A nas saídas de B3,B2,B1,B0.

Os bits Y,Z,A estão na entrada 1 dos MUX de B3,B2,B1. Na entrada 1 do MUX de B0 está B, o bit que entra.

Na entrada 0 dos MUX continua o número R,S,T,U a carregar, o que vai acontecer no próximo clock, pois agora PL é 0 e seleciona estas entradas, colocando R,S,T,U nas entradas de B3,B2,B1,B0.

Quadro IV – 3º Clock. Os valores R,S,T,U nas entradas das Básculas são memorizados, passando as suas saídas ater os valores R,S,T,U.

Os bits S,T,U estão na entrada 1 dos MUX de B3,B2,B1. Na entrada 1 do MUX de B0 está A, o bit que entra.

São os bits S,T,U,A da entrada 1, os do deslocamento, que vão ficar nas entradas de B3,B2,B1,B0, pois PL é 1 e seleciona a entrada 1 dos MUX. No próximo Clock serão memorizados nas Básculas estando feita a sua rotação.

Mas nós ficamos por aqui.

Voltando ao nosso circuito de conversão de uma transmissão em paralelo para série, dissemos da última vez que: “Carrega o número a deslocar, desloca-o bit a bit para o circuito em série e no fim volta a carregar outro número”.

E como é que ele sabe que chegou ao fim?

Através de um circuito contador binário, que conta a evolução do deslocamento dos bits e que avisa quando chega ao fim, dando assim sinal para o carregamento de novo número. É o que vamos ver já de seguida.