The Processor (CPU)

At last, here we are, now facing the computer Brain. The processor or CPU (Central Processing Unit) it’s the component which turns the computer different from a calculating machine, or even a washing machine.

And where is the reason for this difference?

The CPU is an integrated circuit that allows the man to grant it different behaviors through programming.

This integrated circuit is composed by multiple logical circuits more or less complex. The introduction of 0 or 1 signals according to specific combinations make it perform operations leading to a specific purpose. When these values are the selection bits of a Multiplexer, they will make it choose one between its different inputs to set in the path that follows. If its the case of a Demultiplexer, they will make it choose from its several outputs the path the program proceeds.

These operations, which result from specific interconnection of the CPU logical circuits, are the instructions. These instructions follow each other in a particular sequence making in the whole what is called a program, that causes the processor to execute with unmeasured speed what man can only do with the speed of its own.

But it was the man’s intelligence who conceived and took advantage of that Integrated Circuit (IC), so that it would help him in a more reliable, controlled and quick fashion, to execute his tasks.

This IC ability to evolve and its links to the outside world are one of the major challenges that the human intelligence faces. The fact that the limit of the evolution of these increasingly small things is as more indefinite as it evolves, is an even greater challenge for those who like to think and use in that sense what God has placed on their shoulders.

But to be able to take advantage of our intelligence to deal with a microprocessor, we need to deeply know what it is, how it works and how we can talk to it. The vocabulary of its language we already know. Now we have to build words with it. Then phrases, the instructions. And finally texts, the such programs.

This was the purpose that took us to start this job: To turn easy for those who are interested to contact with something which is elemental but seems so complex that everyone runs away from it. Actually it is complex, very complex. But its complexity comes from the sum of the most elemental simplicities as with everything in computing, as we insist since we began this work .

We begin this Chapter with a brief description of the computer memory, because the CPU lives in close collaboration with it. All the instructions to be executed and the data that is in operation has to be in memory. The CPU only works with data which is in the main memory.

The CPU is composed by circuits identical to those we have analyze in the previous Chapter, organized into 3 different abstract areas:

- The ALU (Arithmetic and Logic Unit), where are all the circuits that perform arithmetic and logical operations.

- The CPU Registers, which are Edge Triggered Latches (ETL) Registers, where all the elements over which the CPU operates are temporarily stored, such as for instance the data in operation by the CPU, the instructions, the memory addresses being accessed. The registers are at the highest level in the hierarchy of memories.

- The Control Unit, where decisions are made about which path to take in every situation, as will order the instruction of the running program. This unit is mainly composed by Multiplexers ( MUX ) and Demultiplexers ( DEMUX ) which take their decisions according to the control signals which are sent to them by the Decoder in result of the instruction decoding.

It’s a MUX that decides whether it reads or writes in memory . It’s a MUX that chooses the type of operation to perform on the ALU . It’s a MUX that chooses whether the program follows its normal sequence or performs a jump . It’s a MUX that puts the instruction pointer to the next sequential instruction or a jump instruction. And so on.

The MUX, as we have seen, are controlled by selection bits which tell them what the option to choose in each case. How do those selection bits get to the MUX in response to a program? Will it be the programmer job to teach the MUX what to do in each instruction? Yes it is, through the program he develops. But he doesn’t know it when developing the program. It’s the conversion of his program in binary code which will command them. And that’s just what we are going to show how.

Each instruction is composed by an Opcode (Operation Code) and a value which can represent several parameters which we’ll call Constant. The Assembly is a low level programming language whose purpose is to represent the several Opcodes by mnemonics that we understand.

But, as developing programs in Assembly in nowadays computers its almost impossible, these are developed in high level programing languages as C, Java, C#, C++, etc., no matter the machine where they will run in or the Architecture of its CPU. Afterwards these programs are converted in binary executable code, i.e. a set of 0 and 1 digits which are understood and executed by the CPU, the named Opcode and Constant.

All this is documented in this chapter, in which we tried to take to the lowest possible level the possibility of turning understandable these concepts.

We’ve built the CPU Control Unit MUX by MUX with the respective control signals.

We’ve imagined a C language program, we translated it into an Assembly program, into Opcodes, and finally through the decoder to the control signals corresponding to each opcode which wiill execute each instruction.

We created graphics, a total of 23 frames, representing all the operations that the CPU executes to fulfill the program, where we highlight the control signals coming from each opcode and their value, the values in the Registers, In the Data Memory and in the Instructions Memory, explaining their value reason.

To finish the Chapter we will make an approach between our fantasy and the reality and we’ll describe some aspects of a real CPU, the Intel Core i7 Nehalem. We will emphasize the effort of the manufacturers in the parallel and simultaneous execution of the most number of operations through pipeline.

Off course this description will be limited by our present knowledge and by the huge complexity of such a CPU of last generation.

See the global synopsis of this work

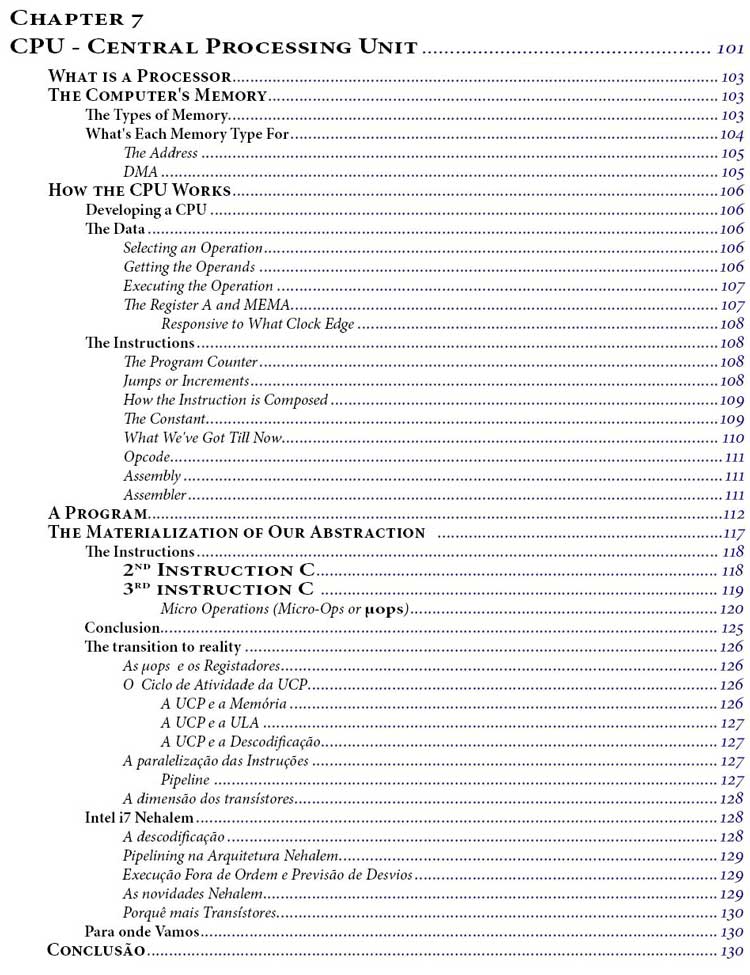

We introduce here the table of contents of the Paper Book to describe the themes approached in this Chapter