A Memória Principal

A Memória Principal ou RAM como é vulgarmente conhecida, tem um nome bem mais comprido do que isso, sendo atualmente de SDRAM DDR3, que significa:.

Synchronized (S) , pois o clock da memória está sincronizado com o da Placa Mãe através do Controlador de Memória (CM).

Dynamic (D), pois a memória principal é composta por células que têm um comportamento dinâmico, isto é, têm que estar permanentemente a ser recarregadas. A célula de memória SDRAM é composta por um transístor e um condensador. É o condensador que armazena o valor do bit (1 se carregado e 0 se descarregado). Ora os condensadores perdem carga, tendo portanto de ser recarregados temporariamente. Daí o nome de dinâmica, dado a esta memória.

RAM significa Random Access Memory ou Memória de Acesso Aleatório, isto é, podemos aceder a qualquer célula em qualquer endereço sem ter que percorrer os anteriores ou seguir qualquer sequência predefinida.

DDR3 significa Double Data Rate ou Taxa de Transferência Dupla de nível 3.

Como vamos ver, a gestão de uma SDRAM é complexa, devido ao grande número de diferentes operações que têm que ser efetuadas sobre a mesma para garantir que a principal, guardar dados para a operação da CPU, possa ser cumprida com eficiência.

Devido a essa complexidade existe o Controlador de Memória (CM), responsável por enviar à memória os sinais que lhe indicam os diferentes tipos de operações a efetuar e como.

Não vamos analisar o CM pois isso está fora do âmbito deste Capítulo, mas vamos analisar como a memória interpreta e executa os sinais que o CM lhe envia, os comandos.

Vamos ver como se organiza fisicamente a memória e como se consegue aceder individualmente a cada uma dos milhares de milhões de células.

Vamos analisar a forma e o funcionamento de uma célula de memória, aquela que contém o valor de um bit. Como será que a carga de um nano condensador consegue ser lida ou mantida, pensando que a sua capacitância é inferior à das linhas que tem que alimentar para poder ser lido e restaurado. E as linhas que tem que alimentar nos circuitos impressos, essas já não nano mas micro linhas em cobre, por forma a que a sua informação chegue ao destino desejado.

Por outra linguagem, como é que um pequeno balde despejado num riacho e depois num rio, consegue fazer-se notar, isto é, fazer saber se estava cheio ou vazio? À partida não parece simples. Bom, e já agora, como é que, depois de o balde se ter despejado para sabermos o que continha, vamos fazer para que o seu conteúdo permaneça como estava, pois a célula guarda um valor que não se pode perder.

Vamos ver como é que circuitos lógicos como o Sense Amplifier e o Buffer Tristate conseguem cumprir as funções necessárias para que o descrito no parágrafo anterior seja possível.

O que é a latência de uma memória, ou seja, o tempo que temos que esperar entre o pedido de um dado e a sua leitura nos pinos do módulo de memória (DIMM).

Do que resulta essa latência, por que razão esse valor pouco variou dos últimos modelos para as primeiras SDRAM em comparação com o aumento das Taxas de transferência.

Vamos tentar reproduzir um imaginário circuito de comando de uma memória SDRAM que cumpra as diversas operações a realizar pela mesma e vamos entender quais são, para que servem e em quer circunstâncias são executadas, tentando pormenorizar cada uma delas em partes do circuito principal onde cada função se cumpre.

Na memória, a lógica temporizada desempenha uma importância fundamental, pelo que vai ser tratada com a máxima profundidade possível, apresentando-se gráficos da evolução do Clock com os seus diversos estados (tempo em baixo, flanco ascendente, tempo em cima e flanco descendente), tentando ligá-los com os diferentes sinais de comando, quando chegam e quando são tratados na memória.

É aí que evidenciaremos as diferentes componentes da latência e como devem ser respeitados os parâmetros de uma memória, cada uma com os seus, que comunica ao CM logo que é ligada.

Vamos também tentar entender quais as principais diferenças da SDRAM para as suas sucessivas evoluções, DDR, DDR2 e DDR3, que erradamente se apontam como tendo frequências elevadíssimas, quando na realidade a frequência de trabalho interna da memória é pouco diferente da SDRAM descrita (dependendo do modelo), aumentando sim a frequência no barramento do circuito impresso que é bombardeado com injeções de dados até 8 vezes por cada ciclo de Clock interno da memória, conseguindo assim taxas de transferência (não frequências) muito maiores.

Ver a síntese global deste trabalho

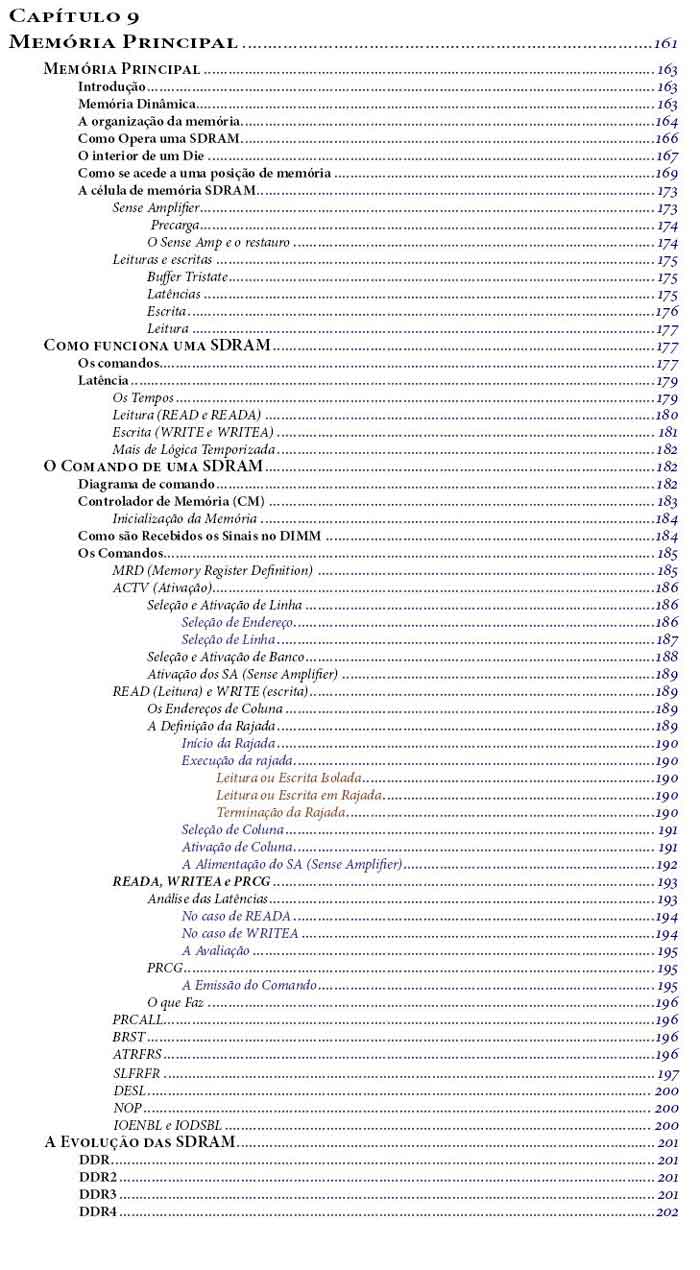

Inserimos de seguida o índice da edição em livro como forma de descrição dos temas abordados neste Capítulo