Barramentos para Transmissões em Paralelo

FSB (Front Side Bus) ou Barramento Frontal

É o conjunto de linhas da placa mãe através das quais o processador comunica com o Chip Northbridge e consequentemente com todos os componentes do computador. Como já referimos antes, é este barramento que limita a frequência de vibração com que o conjunto do computador funciona. A frequência do cristal de quartzo está modulada para a frequência dos barramentos da Placa Mãe. Acima dessa frequência as linhas começam a gerar ruído eletromagnético que pode corromper os valores transmitidos nas linhas mais próximas. Isto para além do time skew, já explicado.

Muito se tem investido no FSB, no sentido de aumentar a quantidade de dados que por ele passam. Aumentando a largura da faixa de dados, ou seja, o número de linhas que os suportam, aumentando o número de dados por ciclo através do Double Data Rate e do Quad Data Rate (os processadores da Intel transportam 4 conjuntos de dados por ciclo de clock, a que chamam Quad Pumping). A capacidade de transferência de um barramento corresponde ao produto da largura de banda (suponhamos 64 bits), pelo número de dados por ciclo (admitamos 4) e pela frequência de vibração (suponhamos 100 MHz), o que neste caso corresponderia a 3,2 GB/s.

Double data rate

Corresponde ao envio de um bit em cada flanco do sinal de clock, técnica ainda hoje usada nas memórias DDR.

Quad Data Rate ou Quad Pumping

Corresponde ao envio de um bit em cada flanco do sinal de clock e dois outros em pontos intermédios.

E como é que isto se consegue?

Criando um sinal de clock complementar a partir do real e desfasado em 90 graus que permite também envio de bits nos seus flancos ascendente e descendente. Esta técnica era a adotada pela Intel, que assim conseguia quadruplicar a taxa de transferência do seu FSB até a um máximo de 6,4 GB/s.

Barramento de memória

Os slots (ranhuras) destinados à memória RAM que constitui a memória principal estão ligados ao Northbridge por um barramento dedicado. Os chips de memória RAM (com capacidades diversas) estão incluídos em módulos (os pentes de memória) que se inserem nas ranhuras referidas.

O barramento de memória é um barramento de altas frequências de vibração, que atualmente se situam entre os 533 MHz e os 2 GHz (nas recentes DDR3). Esta elevada frequência deve-se à ligação direta das memórias à CPU nas recentes arquiteturas de computadores.

Porque a memória principal é, junto com o processador, um dos principais componentes do computador, funcionando em estreita ligação com a CPU, dela falaremos mais adiante por várias vezes e em várias fases, conforme o nosso conhecimento for evoluindo e aceitando conceitos de maior complexidade.

Barramento PCI

O barramento PCI (Peripheral Component Interconect) veio substituir quase todos os tipos de barramentos de expansão existentes até ao seu desenvolvimento.

Foi criado pela Intel e as suas especificações foram publicadas e entregues a uma organização independente PCI-SIG que a partir de então desenvolveu as sucessivas revisões às especificações para o PCI.

Este facto, aliado às excecionais características técnicas deste barramento face aos existentes, tornaram-no apetecível a todos os fabricantes de Hardware, o que levou a que rapidamente se tornasse um barramento standard em todas as placas mãe.

O PCI é um barramento paralelo a 32 bits que funciona na sua forma básica a uma frequência de 33 MHz. Ao mesmo barramento PCI podem conectar vários slots PCI.

Slot é o termo Inglês para um tipo especial de ficha com forma de ranhura com contactos de ambos os lados, onde as placas de circuito impresso de outros componentes se encaixam através de uma saliência também com contactos de ambos os lados.

Também podem conectar através de barramento PCI componentes residentes na placa mãe. Até à implementação do HL (Hub Link), barramento proprietário da Intel para estabelecer a comunicação dos chips Northbridge e Southbridge (Hubs), era através do PCI que se estabelecia essa ligação. .

Para além das já citadas, outra das razões que levou à adoção universal deste tipo de barramento foi o facto de o mesmo incorporar o padrão PnP (Plug and Play). Aquando do lançamento deste padrão nada se sentiu, mas quando alguns anos depois o Windows 95, pela primeira vez, trouxe suporte ao PnP, o pedido de computadores com barramentos PCI subiu rapidamente fazendo cair o até aí usado barramento ISA.

O barramento PCI liga diretamente ao Southbridge, que faz a gestão da atribuição de linha aos diversos componentes bem como controla a frequência de clock no barramento.

Mais adiante iremos fazer uma pequena abordagem ao padrão PnP, de que o barramento PCI foi precursor e que domina os computadores dos nossos dias.

O Barramento AGP

A rápida evolução das placas de vídeo, com a consequente solicitação de maiores capacidades ao barramento de transporte levou à criação de um outro barramento chamado AGP (Accelerated Graphics Port) com performances muito mais adaptadas às necessidades das solicitações de gráficos em 3D.

O AGP mais não era do que um barramento PCI, do qual diferia em duas características essenciais:

- Dispunha de um barramento dedicado para cada slot AGP (uma em cada placa mãe).

- Dispunha de uma aceleração, como o próprio nome indica, que lhe permitia, com a mesma frequência do PCI, transferir 1,2 4,ou 8 bits por linha no mesmo ciclo de clock. Isto era conseguido desenvolvendo sinais de clock a partir do primeiro e desfasados dele, que transmitiam nos seus flancos ascendente e descendente.

Não vamos falar mais deste barramento, porque ele já foi substituído pelo barramento PCI Express.

Barramento LPC

O LPC (Low Pin Count) é usado para conectar o BIOS e o Súper I/O chip à Ponte Sul. A sua principal vantagem é a simplicidade e elementaridade resultantes de ser suporte para periféricos lentos e mais antigos, necessitando de muito menos conexões, sendo portanto fácil de rotear numa placa mãe já sobrecarregada de conexões. A frequência de clock que usa corresponde à do barramento PCI ou 33 MHz. A taxa de transferência típica é de 2,56 MB/s.

Barramentos para Transmissões em Série

O PCIe (PCI express)

Porquê substituir uma técnica de transmissão de 32 bits de cada vez por uma outra que transmite só 1 bit de cada vez?

A transmissão em série é efetuada de forma diferencial, isto é, através de dois cabos, trançados e balanceados, isto é, com iguais impedâncias ao longo do seu comprimento e iguais impedâncias em relação à terra e para com outros circuitos, a que chamaremos D+ e D- .

Há vários métodos de transmissão diferencial. Para o PCIe o método consta da introdução de um determinado valor de voltagem em um dos cabos. Seja AV o valor de voltagem para o estado lógico 1 e 0V o valor para o estado lógico 0.

Quando se pretende enviar 1 injeta-se AV em D+ e 0V em D-. A leitura é feita por subtração dos dois valores e neste caso dará AV sendo D+>D- e o valor lógico correspondente 1.

Quando se pretende enviar um 0, injeta-se AV em D- e 0V em D+. A leitura resultante da subtração dos dois valores é -AV, sendo D+ No final existe um diferencial entre os estados lógicos 1 e 0 de AV-(-AV)= 2AV, o que reduz substancialmente a interferência de ruído. O ruído, a existir, introduzir-se-á nos dois cabos de igual forma e ao ser feita a subtração dos dois valores no recetor, é anulado. Na transmissão diferencial o que interessa é o sinal e a diferença de potencial. Pode-se assim aumentar a frequência até valores que podem chegar à frequência dos processadores. Em lugar de dois cabos temos quatro e consequentemente uma transmissão unidirecional em cada par e simultaneamente nas duas direções nos dois pares. A este conjunto de cabos chama-se Lane e é composta por dois Links. Podem-se acrescentar mais Lanes, até um total de 32 tendo situações de 1, 2, 4, 8, 16 e 32 Lanes, que dão origem às designações PCIe x1, PCIe x2, PCIe x4, PCIe x8, PCIe x16 e PCIe x32. Esta última ainda não foi posta em prática. A transmissão PCIe é uma transmissão ponto a ponto, isto é as linhas que servem cada dispositivo são-lhe exclusivas e não compartilhadas. Nesta primeira versão o PCIe pode chegar a taxas de transferência de 8GB/s. Foi na sequência do desenvolvimento destas tecnologias e da sua maior solicitação que a AMD adotou o Barramento Hyper Transport como substituto do FSB. SATA (Serial Advanced Technology Attachment), é uma tecnologia de transferência de dados usada para comunicações do computador com dispositivos de armazenamento de massa, concretamente Discos Rígidos e Discos Óticos (CD e DVD). Corresponde a mais uma evolução de paralelo para série do tipo de barramentos que suportam transferências de grande volume e que portanto necessitam de taxas de transferência mais elevadas. Concretamente corresponde à evolução da tecnologia ATA (Advanced Technology Attachment), também conhecida por IDE (Integrated Drive Electronics) que foi renomeada para PATA (Paralel ATA) precisamente para se distinguir de SATA (Serial ATA). As ligações SATA comunicam diretamente com um controlador AHCI (Advanced Host Controller Interface) que deverá estar residente no Chipset da Placa Mãe. E daí comunicam com a CPU ou diretamente com a memória através de DMA (Direct Memory Access). A 2ª geração ou SATA II ou SATA 3 Gbit/s, por ser esta a sua taxa de transferência, é ainda encontrada muito frequentemente em muitos computadores, mesmo alguns em venda, uma vez que os Discos Rígidos magnéticos ainda não absorveram totalmente a sua largura de banda. A atual geração desta tecnologia Sata III ou SATA 6 Gbit/s, já é a mais implementada nos PC de maior performance atualmente comercializados, pois os atuais Solid State HD (SSD) baseados em tecnologia Flash, já excedem as capacidades do SATA II. Esta ligação destina-se a componentes ligados por cabo à Placa Mãe, internos à caixa do computador. A transmissão série diferencial usada por esta tecnologia baseia-se em 1 Lane (2 Links unidirecionais), portanto Full duplex e o controlo diferencial utilizado é o correspondente ao que se vai descrever para o barramento Hyper Transport. USB é uma tecnologia dirigida à conexão de periféricos externos ao computador. A transmissão de dados é feita em série, half duplex, isto é, em uma direção de cada vez e bit a bit. O USB surgiu na sequência da grande expansão dos computadores pessoais e proveio da necessidade de facilitar a ligação de periféricos externos diversos. Esta tecnologia foi concebida na ótica do conceito Plug and Play (PnP). Antes do USB aparecer, as ligações dos computadores ao exterior estavam limitadas a duas portas série, uma porta paralela e alguns slots PCI de expansão na placa mãe, onde se podiam instalar placas para ligações exteriores específicas, como vídeo, rede, som e outros. Eram instalações complicadas e que exigiam normalmente a intervenção de técnicos especializados pois era necessário definir uma série de parâmetros para cada componente, como IRQ por exemplo e manobrar “jumpers” (este era o nome de uns pequenos pinos que serviam para unir dois contactos) que vinham nas placas ou equipamento. Se algo não fosse devidamente implementado eram gerados conflitos que podiam impedir o funcionamento desse periférico ou mesmo mais, podendo até parar o computador. O conceito PnP veio revolucionar estes problemas pois facilitava a instalação dos periféricos por parte de qualquer utilizador com algum conhecimento e medianamente arrojado. Foi a associação da tecnologia USB ao conceito PnP que veio de vez vulgarizar a ligação de quaisquer componentes a um computador. O USB permite a ligação de vários componentes a partir de um Master Hub, podendo ser intercalados mais hubs, dos quais poderão derivar mais ligações até um máximo de 127 componentes num máximo de cinco hubs (um hub é, neste caso, um desmultiplicador de portas USB). A sua expansão é feita mediante uma topologia em árvore e parte do Host, o Master HUB que se encontra no Southbridge e que faz a gestão de todos os equipamentos ligados a partir dele, até um máximo de 7 níveis de Hubs, incluindo o próprio. O tipo de conector é comum a todos os equipamentos que usem esta tecnologia, tornando assim fácil a conceção desses periféricos no que diz respeito ao suporte por parte dos sistemas operativos e do hardware. Foi criado um padrão que permite ao sistema operativo e à placa mãe identificarem o tipo de equipamento, suas necessidades de alimentação, suas necessidades de banda e outros, logo que ele é detetado e identificado. Quando o computador arranca, os dispositivos USB a ele conectados são detetados e é-lhes atribuído um número. Cada vez que um componente é conectado ao computador por uma porta USB é detetada a sua presença e o controlador e o SO verificam se já dispõem das suas drivers ou se estão incluídas no próprio e colocam-no em condições de ser utilizado. Se as drivers do componente não estão disponíveis é solicitado ao utilizador a introdução do disco contendo as mesmas, fornecido pelo fabricante. Mais recentemente o próprio SO consulta uma base onde dispõe da grande maioria de drivers. A versão atualmente mais vulgarizada nos computadores em funcionamento e em dispositivos móveis é a 2.0, que permite ligações com uma taxa de transferência de 480 Mbits/s (80 MB/s) contra os 12 Mbits/s (1,5 MB/s) da anterior versão 1.1, completamente abandonada. Já instalada em quase todos os PC novos existe agora a nova versão USB 3.0, que tem taxas de transferência de 3.2 Gbits/s (400 MB/s) em full duplex (simultaneamente nos dois sentidos), o que supera as taxas de transferência atualmente conseguidas pelos discos rígidos existentes no mercado. A BIOS é o programa central que habilita o PnP. Lê o ESCD (Extended System Configuration Data), isto é, em termos para nós legíveis, consulta um arquivo que dá pelo pomposo nome de ESCD, que contém informações sobre os dispositivos PnP instalados. Um Sistema Operativo compatível com PnP completa o processo iniciado pelo BIOS. O PnP automatiza as seguintes tarefas: E como é que isto funciona? Durante o Boot, o BIOS identifica todo o hardware presente e pede a identificação a cada um. Quando a obtém verifica se já consta do ESCD. Se não, o BIOS atribui-lhe IRQ, DMA, endereço de memória e configuração de I/O. E regista os dados no ESCD. Posteriormente o Sistema Operativo (SO) consulta o ESCD, verifica os componentes e carrega os drivers (pequenos programas de identificação do componente perante o SO) necessárias ao seu reconhecimento ou pede a sua instalação através de disco fornecido pelo fabricante caso os respetivos drivers ainda não estejam instalados. Atualmente é normal que os drivers venham incluídos no componente de forma a serem lidos pelo Sistema Operativo aquando da sua primeira utilização. O próprio SO, como é o caso, p.e. dos Windows 7 e 8, tem acesso a uma gigantesca base de dados onde estão todas as drivers de equipamentos criadas e fornecidas pelos fabricantes para esse SO. Por questões de segurança a introdução de drivers pelo utilizador através de discos está a ficar extremamente restrita pelos SO. As drivers instalam-se no Kernel do SO, uma área extremamente sensível para a segurança do computador. Após vários casos de severas ameaças à segurança de computadores por este método os SO criaram esta forma de defesa. Porque pelo FSB têm de passar todas as comunicações da UCP com a Memória Principal, com a placa de vídeo, com a placa de som, com o Disco Rígido e todos os outros periféricos, este sempre tem sido um gargalo complicado para as constantes evoluções dos processadores, das memórias, das placas de vídeo e outros componentes. Os enormes avanços conseguidos pelas placas de vídeo suportadas pelos barramentos PCI express, permitiam transferências de dados, numa primeira fase, de 8 GB/s no máximo, o que só por si já excedia a capacidade do FSB. Isto para não falar nos constantes acessos que o processador tem de fazer à memória principal, no seu constante aumento de capacidade e no seu constante aumento de taxas de transferência (DRAM, DDR, DDR2, DDR3). Não há qualquer dúvida de que o FSB estava a funcionar como um travão ao crescimento de novas tecnologias, pois não permitia a sua exploração para além de valores que se estavam a tornar irrisórios face ao desenvolvimento de todos os componentes. A tendência de evolução dos barramentos está a ser, a todos os níveis, a passagem de paralelo para série. Serial ATA (SATA) e PCI express (PCIe) representam evoluções dos seus antecessores PATA e PCI de transmissões em paralelo para transmissões em série. Para não falarmos do USB e do Firewire que já nasceram como comunicações em série e que experimentaram e continuam a experimentar evoluções enormes, especialmente no campo do USB. Talvez por ser o fabricante com as mais baixas taxas de transferência no FSB, foi a AMD a primeira a investir numa arquitetura completamente diferente na transmissão de dados no FSB e no Layout de organização dos barramentos na Placa Mãe. A tecnologia Hyper Transport foi adotada pela AMD e criada por um consórcio da AMD, da NVidia e da Apple. O barramento Hyper Transport foi implementado pela AMD em conjunto com a Arquitetura AMD64. É uma transmissão série ponto a ponto com envio de dois dados por pulso de clock e full duplex. É um barramento com lanes de dois links, um em cada direção. A transmissão é série diferencial, mas o método de transmissão é diferente do descrito para o PCIe. O barramento Hyper Transport tem uma filosofia de transmissão por pacotes de n palavras de 32 bits, independentemente da largura de links da ligação. A transmissão é sempre iniciada por uma palavra que contém o código de transmissão. O número de bits é sempre múltiplo de 32, independentemente do tamanho de dados a transmitir. O barramento Hyper Transport vem vocacionado para substituir o FSB mas também para a comunicação entre processadores em multiprocessamento ou núcleos de processadores em multicore. Junto com o barramento Hyper Transport a AMD implementou a sua arquitetura AMD64 que consiste na transferência do controlador de memória para o chip da CPU com acessos diretos por duplo canal aos DIMM DDR2, alterando também o layout das placas mãe, conforme se pode ver na Figura 1. É a versão da Intel para substituir o FSB. Em tudo semelhante ao HyperTransport não existe contudo qualquer compatibilidade entre as duas soluções. É uma transmissão em série, ponto a ponto, com dois dados por ciclo de clock e Full duplex. É composto por 20 linhas e a transmissão é feita em blocos de 80 bits, que são enviados em dois ciclos de clock. Desses 80 bits, 8 são para controlo de erro, 8 são para cabeçalho do link layer. Trabalhando a uma frequência de 3,2 GHz consegue uma taxa de transferência útil de 25,6 GB/s em ambos os sentidos (full duplex). Será também através deste tipo de barramento que os vários núcleos de uma CPU multi nuclear se interligarão. Este barramento surge na sequência de uma nova arquitetura desenhada pela Intel, a arquitetura Nehalem, da qual falaremos nos nossos casos de estudo ao longo deste trabalho. As comunicações com a memória foram retiradas do Northbridge e passaram para o chip da CPU por incorporação do controlador de memória no mesmo, alterando assim também o layout das suas placas mãe para o da Figura 1. PCH (Platform Controller Hub) resulta do esvaziamento das funções do Northbridge, devido à incorporação das mesmas no chip da CPU, que passou a receber também as lanes PCIe, para além da ligação direta à memória pela incorporação do controlador de memória. Assim, o Southbridge passou a incorporar todas as funções de I/O e de controlo das restantes funcionalidades da placa mãe. Para além das que já lhe eram próprias, passou a incorporar o RTC (Real Time Clock), as funções do Súper I/O, o chip Ethernet e outros, adquirindo também o nome de PCH (Hub Controlador da Plataforma), consistente com as suas novas funções. O PCH dispõe também do controlador de display, pois é a ele que compete a comunicação com o display nos casos em que o Chip da CPU já tenha incorporado o processador gráfico e em que não exista placa de Vídeo. Esta alteração deu-se ainda com a arquitetura Nehalem e é suportada inicialmente pelos processadores Intel Atom, Intel Core i3, Intel Core i5 e Intel Core i7 com exceção das séries 9xx. O PCH dispõe de duas comunicações com a CPU: Tanto o DMI como o FDI foram sendo introduzidos nas diferentes inovações do Intel Core i7, com a passagem da arquitetura Nehalem para as arquiteturas Sandybridge e Ivybridge e com a diminuição da dimensão dos transístores que nos primeiros i7 era de 45 nm e agora se encontra em valores de 22 nm. A Figura 2 tenta ilustrar o que será o Layout de uma atual placa mãe. Serial ATA ou SATA

USB (Universal Serial Bus)

Plug and Play (PnP)

A evolução do Barramento FSB

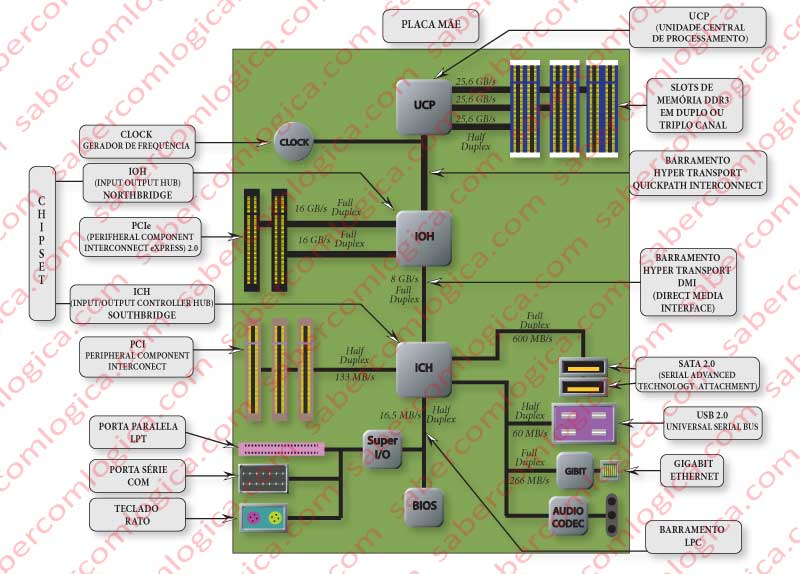

Barramento Hyper Transport

QuickPath Interconnect

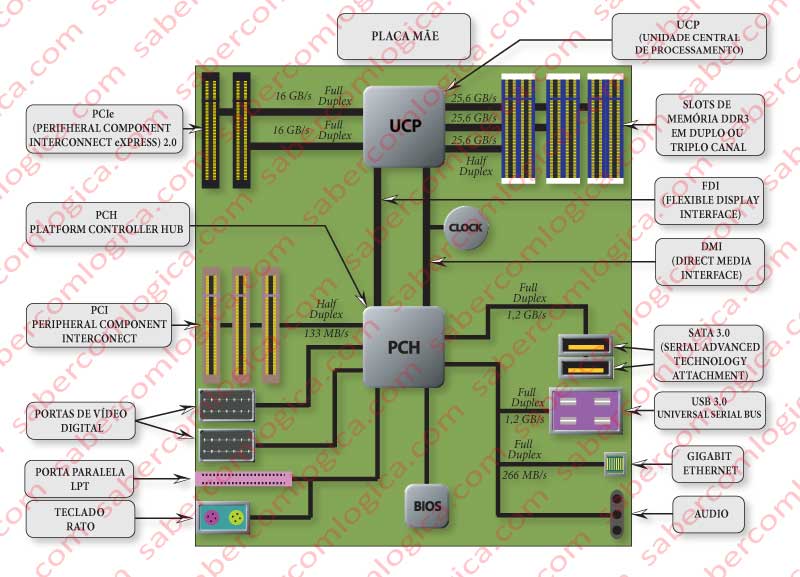

PCH