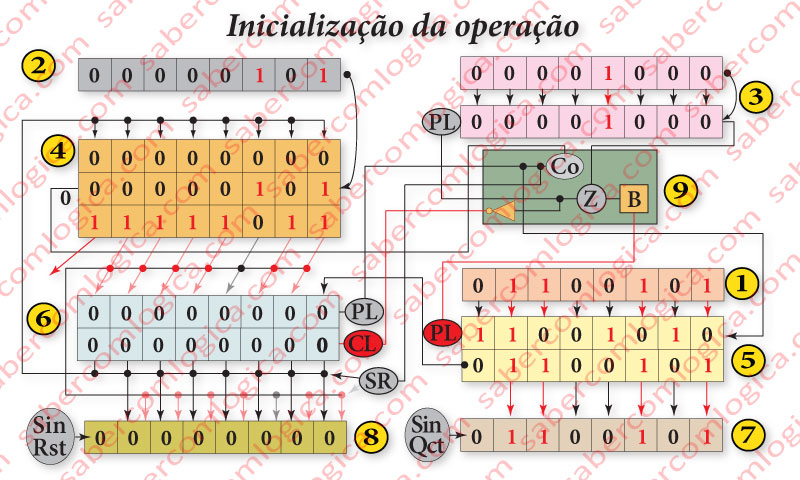

Executando a Operação

Inicialização

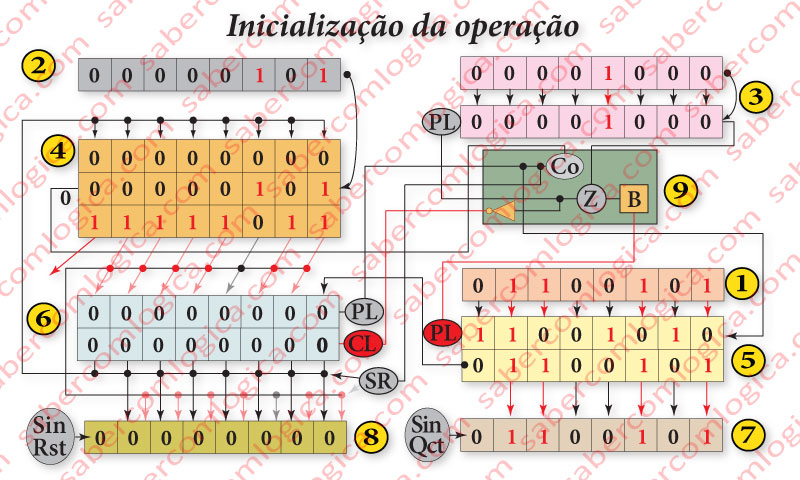

Nesta primeira figura vamos identificar os símbolos e componentes utilizados e atribuir-lhes valores iniciais Quanto aso símbolos, teremos:

- Sin Qct – Sinal do quociente

- Sin Rst – Sinal do resto.

- B – Circuito de tratamento da deteção de zero.

- CL – Sinal de Clear para as básculas (ativo a 0)

- Co – Carry out do circuito de subtração.

- Z – Sinal indicativo de Deteção de Zero (ativo a 1).

- PL – Sinal indicativo da seleção de Carregamento em Paralelo (ativo a 1). Vamos chamar PL3 ao do Contador 3, PL5 ao do Registo 5 e PL6 ao do Registo 6.

E quanto aos componentes:

- 1 – Representa o Circuito 1 que contém o valor do dividendo, já inteiro sem sinal, 01100101(101). Está ligado à entrada carregamento do MUX do Registo 5.

- 2 – Representa o Circuito 2 que contém o valor do divisor já inteiro sem sinal, 00000101(5). Está ligado ao 2º operando do Somador 4.

- 3 – Representa o Contador 3.

A linha de cima contém as iterações da operação para carregamento aquando da deteção de Zero. No nosso caso 00001000(8) os bits do dividendo.

A linha de baixo contém o valor memorizado. Agora carregou o número de iterações 00001000(8). - 4 – Representa o Somador4.

A linha de cima contém o 1º operando que vem sempre do Registo 6. Na inicialização será 00000000(0).

A linha do meio contém o divisor que aqui permanece inalterado até ao fim da operação com o valor 00000101(5).

A linha de baixo contém o resultado da operação que está ligado à entrada carregamento do Registo 6 da forma descrita na sua implementação. Neste passo é 11111011(-5) e é irrelevante.

À esquerda sai o Co da operação, que vai ligar ao Quadro 9. Neste passo tem o valor 0 (não cabe). - 5 – Representa o Registo 5.

A linha de cima contém o valor que PL5 está a selecionar na entrada do MUX para entrar no próximo clock (rotação ou carga). Neste caso é uma rotação do valor memorizado, 11001010.

O bit de menor ordem não é o que vai entrar, pois só junto à queda do clock se vai conhecer o seu valor. É quando chega o nosso corredor de estafetas.

A linha de baixo contém o valor memorizado. É iniciada com o carregamento do valor do dividendo mostra o valor 01100101(101). Os dígitos admitidos para o quociente durante a operação são evidenciados a negrito. - 6 – Representa o Registo 6.

A linha de cima contém o valor da entrada do MUX que PL6 está a selecionar para o próximo clock (rotação ou carga). Neste caso é um deslocamento do valor memorizado 00000000(0), pois o bit que vai entrar é 0.

A linha de baixo contém o valor memorizado. É iniciado por um Clear (CL), pelo que o seu valor nesta fase é 00000000(0). Os bits admitidos são evidenciados a negrito. - 7 – Representa o Circuito 7. Durante a operação vai mostrando valores irrelevantes. Só no final mostrará o valor do Resultado da operação.

- 8 – Representa o Circuito 8. Durante a operação vai mostrando valores irrelevantes. Só no final mostrará o valor do Resto da operação.

- 9 – Representa a Unidade de Controlo 9, que não apresenta valores. Só os indica pela cor das linhas.

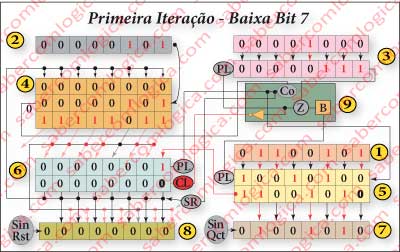

Primeira Iteração

Na subida do Clock:

O Registo 6 desloca à esquerda e admite o bit de ordem 7 do Registo 5, que tinha ficado na sua entrada no final do passo anterior. É aqui que baixa o 1º dígito do dividendo (0). O Contador 3 decrementa uma unidade e fica a marcar 00000111(7).

Com o Clock em alta:

O 1º operando do Somador4 assume o valor das saídas do Registo 6, apresentando o resultado da operação do Quadro 7 do algoritmo, 0 11111011. O resultado é irrelevante porque o divisor não cabe. Co é 0, ficando o seu valor preparado para entrar no Registo 5.

Na queda do Clock:

O Registo 5 admite o bit recém-chegado do Somador 4 com o valor do Co, como 1º dígito do quociente (0) quando desloca à esquerda.

Com o Clock em baixa:

Após o deslocamento à esquerda no Registo 5 o novo valor no seu bit de maior ordem, o bit de ordem 6 do dividendo, propaga-se para o valor do bit de menor ordem da entrada do Registo 6, onde fica à espera de nova subida do clock para nele ser memorizado, isto é, à espera de nova iteração para ser baixado.

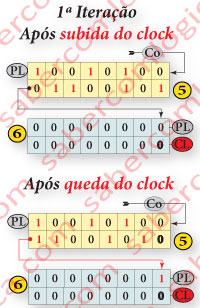

Pode acompanhar-se com a Figura 1 a evolução com o Clock dos valores no Registo 5 e no Registo 6.

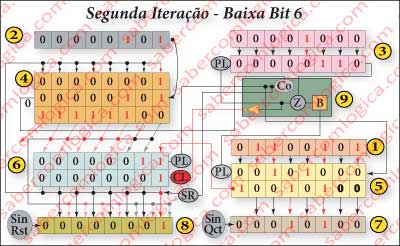

Segunda Iteração

O Contador 3 decrementa e indica 00000110(6).

O Registo 6 desloca à esquerda e admite o bit de ordem 6 do dividendo, i.e. baixa o seu 2º dígito (1) e envia o resultado ao 1º operando do Somador 4, onde se realiza a operação do Quadro 6 do algoritmo.Não cabe.

O resultado é irrelevante, Co é 0 e o seu valor vai ser admitido pelo Registo 5 como 2º dígito do quociente (0) quando desloca à esquerda e coloca o bit de ordem 5 do dividendo na entrada do Registo 6.

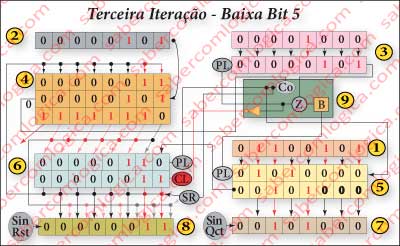

Terceira Iteração

Terceira Iteração

O Contador 3 decrementa e indica 00000101(5). O Registo 6 desloca à esquerda e admite o bit de ordem 5 do dividendo, i.e. baixa o seu 3º dígito (1) e envia o resultado ao 1º operando do Somador 4, onde se realiza a operação do Quadro 5 do algoritmo. Não cabe.

O resultado é irrelevante, Co é 0 e o seu valor vai ser admitido pelo Registo 5 como 3º dígito do quociente (0) quando desloca à esquerda e coloca o bit de ordem 4 do dividendo na entrada do Registo 6.

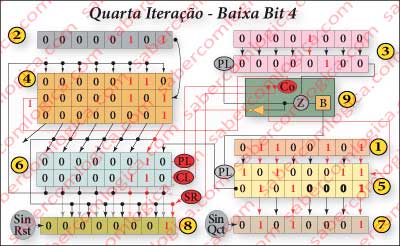

Quarta Iteração

O Contador 3 decrementa uma unidade e fica a marcar 00000100(4).

O Registo 6 admite o bit de ordem 4 do dividendo, i.e. baixa o seu 4º dígito (0) e envia o resultado ao 1º operando do Somador 4, onde se realiza a operação do Quadro 4 do algoritmo com o Resultado 1 00000001. Desta vez cabe.

Co é 1 e PL6 passa a 1, selecionando para as entradas do Registo 6 o valor do Resultado deslocado à esquerda. O Registo 5 admite o bit recém-chegado com o valor do Co como 4º dígito do quociente (1) quando desloca à esquerda e coloca o bit de ordem 5 do dividendo na entrada 0 do Registo 6.

Na Figura 2 pretendemos ilustrar as alterações nas diversas fases do clock nesta 4ª iteração, não visíveis nos quadros das situações finais. Para isso incluímos as situações final da 3ª e inicial da 5ª iterações. Vamos evidenciar o mais significativo:

Após a subida do clock e propagação das alterações resultantes, o bit na entrada de ordem 0 do Registo 5 muda de valor. Na subida do clock muda o 1º operando devido ao deslocamento à esquerda do Registo 6. Na propagação destes valores, a operação realizada no Somador 4 alterou valor do seu Co que por sua vez se vai propagar e alterar o valor do bit de ordem 0 do Registo 5, onde fica a aguardar pela queda do clock.

O valor que PL6 apresenta nos quadros finais não indica o que fez nesse ciclo, mas sim o que vai fazer no próximo. Note-se que PL6 só vai mudar após a propagação de Co provocando a carga do resultado da operação no Registo 6 na próxima subida do clock.

Após a queda do clock e propagação dos valores resultantes o bit de ordem 0 do Registo 6 muda, neste caso de 0 para 0 e por acaso mantendo o valor. Na queda do clock o Registo 5 deslocou à esquerda e colocou novo valor no seu bit de ordem 7, que se propagou ao bit de ordem 0 do Registo 6, aguardando pelo nova subida do clock.

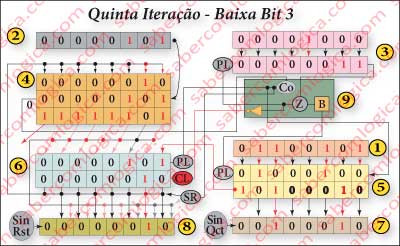

Quinta Iteração

Quinta Iteração

O Contador 3 decrementa e indica 00000011(3).

O Registo 6 carrega o resultado do ciclo anterior do Somador 4, desloca à esquerda e admite o bit de ordem 3 do dividendo, i.e. baixa o seu 5º dígito (0) e envia o resultado ao 1º operando do Somador 4, onde se realiza a operação do Quadro 3 do algoritmo.

Não cabe.

O resultado é irrelevante, Co é 0 e o seu valor vai ser admitido pelo Registo 5 como 5º dígito do quociente (0).

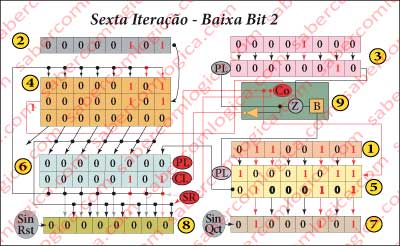

Sexta Iteração

Sexta Iteração

O Contador 3 decrementa e indica 00000010(2).

O Registo 6 desloca à esquerda e admite o bit de ordem 2 do dividendo, i.e. baixa o seu 6º dígito (1) e envia o resultado ao 1º operando do Somador 4, onde se realiza a operação do Quadro 2 do algoritmo.

Agora cabe.

PL6 passa a 1 e seleciona o resultado da operação. Co é 1 e o seu valor vai ser admitido pelo Registo 5 como 6º dígito do quociente (1).

Sétima Iteração

O Contador 3 decrementa e indica 00000001(1). O Registo 6 carrega o resultado do ciclo anterior do Somador 4, desloca à esquerda e admite o bit de ordem 1 do dividendo, i.e. baixa o seu 7º dígito (0) e envia o resultado ao 1º operando do Somador 4, onde se realiza a operação do Quadro 1 do algoritmo. Não cabe, o resultado é irrelevante, Co é 0 e o seu valor vai ser admitido pelo Registo 5 como 7º dígito do quociente (0). Na entrada 0 do Registo 6 vai ficar o bit de ordem 0 do dividendo

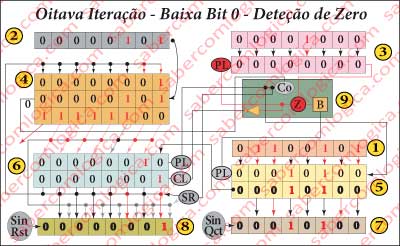

Oitava Iteração

Oitava Iteração

O Contador 3 vai chegar a 0.

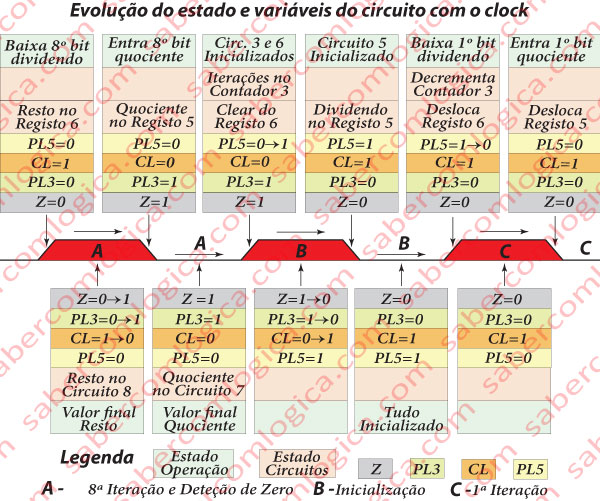

A Figura 3, que ilustra a evolução das variáveis e do estado do circuito desde o flanco ascendente do clock do ciclo de deteção de zero até ao flanco descendente do clock do ciclo da 1ª iteração, vai ajudar a acompanhar esta descrição.

Na subida do Clock:

O Contador 3 decrementa e coloca 00000000(0) nas suas saídas. O Registo 6 desloca à esquerda e admite o bit de ordem 0 do dividendo, i.e. baixa o seu 8º dígito (1).

Com o Clock em alta:

O valor nas saídas do Contador 3 propaga-se à sua porta NOR e dá-se a Deteção de Zero. Z passa a 1, propaga-se ao Circuito 9b onde fica na entrada da Báscula de atraso, coloca PL3 a 1 e CL a 0 (CL=¬Z).

O valor nas saídas do Registo 6 propaga-se à entrada 0 do MUX do Circuito 8 como 1º valor 00000001 para o Resto e ao 1º operando do Somador 4, onde se realiza a operação do Quadro 0 do algoritmo. O divisor não cabe.

O Resultado propaga-se à entrada 1 do MUX do Circuito 8 como 2º valor 11111100 para o Resto.

O Co é 0 e o seu valor propaga-se à entrada 0 do Registo 5 e coloca SR a 0, selecionando a entrada 0 (valor memorizado no Registo 6) do MUX do Circuito 8 onde fica o valor final do Resto.

Na queda do Clock:

Quando desloca à esquerda, o Registo 5 admite o bit recém-chegado do Somador 4 com o valor do Co, como 8º dígito do quociente (0). O valor final do quociente está agora memorizado neste Registo.

Com o Clock em baixa:

O valor memorizado no Registo 5 propaga-se ao Circuito 7 onde fica o valor final do Quociente.

No final desta 8ª iteração e após a Deteção de Zero as variáveis ficaram como segue:

Z=1, PL3=1, PL5=0 e CL=0

prontas para a inicialização, que vamos repetir com incidência na variação do valor das variáveis.

Inicialização após detecção de zero

Na subida do Clock:

O valor de CL é 0, por isso é feito um Clear ao Registo 6.

O valor de PL3 é 1 por isso o valor de iterações é carregado no Contador 3.

Com o Clock em alta:

O valor das saídas do Contador 3 propaga-se à sua porta NOR, Z passa a 0 e propaga-se ao Circuito 9b

Z fica à entrada da Báscula de atraso, coloca PL3 a 0 e CL a 1. A saída da Báscula de atraso passa a 1 e propaga-se até PL5, que também passa a 1.

Na queda do Clock:

Com PL5 a 1 o Registo 5 carrega o valor do dividendo.

Com o Clock em baixa:

O bit de maior ordem do Registo 5 propaga-se ao bit de menor ordem do Registo 6 onde aguarda como o 1º dígito do dividendo o início do novo ciclo. O circuito está totalmente inicializado. O valor das variáveis é:

Z=0, PL3=0, PL5=1 e CL=1

Primeira Iteração (Nova Operação)

Com a subida do Clock a saída da Báscula de atraso do Circuito 9b passa a 0 e propaga-se a PL5 que assim passa a 0. As variáveis ficam:

Z=0, PL3=0, PL5=0 e CL=1

valores estes que vão manter até à próxima Deteção de Zero.