Transistor CMOS

Fabrico de um CMOS

O fabrico destes transístores é muito semelhante ao que vimos para os transístores nMOS.

Mas vamos percorrê-lo passo a passo com a ajuda dos quadros junto. Estes quadros são em número muito mais reduzido porque resolvemos acumular muitas fases em cada quadro, fazendo essencialmente sobressair a forma de fabricação de um transístor que engloba dois opostos entre si, um nMOS e um pMOS.

Quadro 1 – As bolachas retiradas do lingote de silício são polidas e limpas de qualquer impureza.

Quadro 2 – (1)Procede-se à oxidação da superfície da bolacha. O dióxido de silício (SiO2) é utilizado como camada de proteção para a superfície ultra limpa da bolacha de silício, assim como camada isoladora.

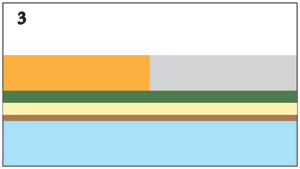

Quadro 3 – (1)Segue-se a deposição de uma camada de Polissílico seguida de outra de nitrato de silício (Si3N4). (2)Procede-se à deposição de uma camada de produto fotossensível e resistente à ação dos agentes corrosivos do etching, sobre as anteriores. (3)Por um processo de Fotolitografia procede-se à exposição da bolacha à luz UV, através das máscaras previamente desenvolvidas que definem a localização dos poços n-dopados onde vão ser criados os pMOS. (4)Remoção do material fotossensível exposto.

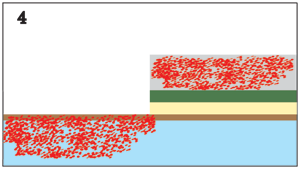

Quadro 4 – (1)Remoção por etching das camadas de Si3N4 e Polissílico nas zonas não protegidas pela camada resistente ao etching. Nessas zonas fica de novo exposto o SiO2. (2)Bombardeamento e implantação de átomos de Fósforo, que penetram através da camada fina de SiO2, sendo retidos pelo Si3N4 nas zonas onde este não foi removido. Os átomos de Fósforo contém excesso de eletrões (mais eletrões do que protões) proporcionando assim a criação da camada N (Negativa), após a sua incorporação, na estrutura cristalina.

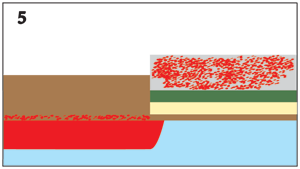

Quadro 5 – (1)O processo de ionização é seguido por um recozimento a altas temperaturas, com o fim de reconstruir as estruturas cristalinas e incorporar os átomos nela implantados. Devido à sua difusão os átomos de Fósforo são adicionados à estrutura da bolacha, criando assim o poço n-dopado. (2)Deposição sobre a camada de SiO2 exposta de uma outra camada de SiO2 de muito maior espessura. A proteção do Si3N4 faz com que só os topos do Polissílico sejam afetados por esta deposição, protegendo assim as partes da bolacha que não se pretendem afetadas.

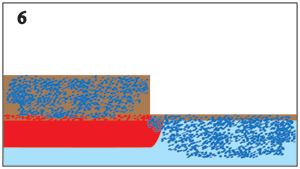

Quadro 6 – Remoção da parte do material fotossensível não exposto por processos químicos próprios. (2)Remoção por etching, das camadas de Si3N4 e Polissílico nas zonas abaixo daquela. Nessas zonas fica de novo exposto o SiO2. (3)Bombardeamento e implantação no silício de átomos de Boro sobre toda a bolacha. Os átomos penetram através da camada mais fina de SiO2 mas são retidos e anulados pela sua camada mais espessa Os átomos de Boro contém lacunas na sua estrutura (falta de eletrões) proporcionando assim a criação da camada P (Positiva) após a sua incorporação na estrutura cristalina.

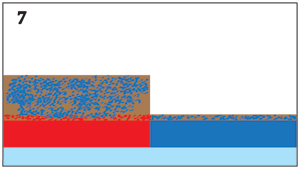

Quadro 7 – Recozimento a altas temperaturas para reconstrução das estruturas cristalinas e incorporação dos átomos na estrutura cristalina. Devido à sua difusão, os átomos de Boro são adicionados à estrutura da bolacha, criando assim o poço p-dopado.

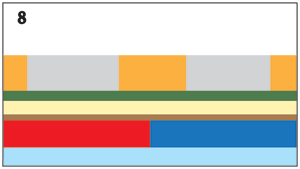

Quadro 8 – (1)Remoção total das camadas de SiO2 por etching. (2)Deposição de uma fina camada de SiO2 totalmente renovada. (3)Deposição de uma camada de Polissílico seguida de outra de Si3N4. (4)Deposição de uma camada de produto fotossensível sobre as anteriores. (5)Exposição da mesma por fotolitografia à luz UV, através de uma máscara que vai revelar as zonas fora dos transístores.

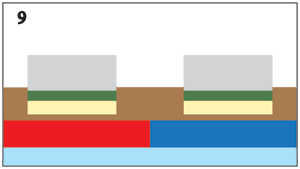

Quadro 9 – (1)Remoção do material fotossensível exposto. (2)Remoção por etching das camadas de Si3N4 e Polissílico nas zonas não protegidas pela camada resistente ao etching. Nessas zonas fica de novo exposto o SiO2. (3)Sobre este é feita a deposição de uma camada mais espessa do mesmo SiO2.

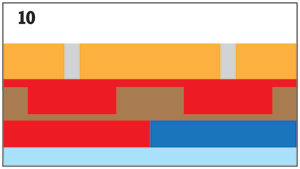

Quadro 10 – (1)Remoção do material fotossensível não exposto, por processos químicos próprios. (2)Remoção por etching das camadas de Si3N4 e Polissílico nas zonas agora desprotegidas. (2)Remoção e imediata recolocação de uma pequena lâmina da camada de SiO2 que assim ficará renovada e totalmente limpa. (3)Deposição de uma camada de polissílico n-dopado, por bombardeamento com átomos de fósforo ou por difusão através do gás que origina a sua formação. (4)Deposição de uma camada de material fotossensível. (5)Exposição desta camada à luz UV através de uma máscara que define as portas dos transístores.

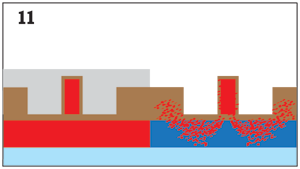

Quadro 11 – (1)Remoção do material fotossensível exposto. (2)Remoção por etching da camada de Polissílico nas zonas não protegidas. Estão assim criadas as Portas dos transístores nMOS e pMOS em polissílico n-dopado. (3)Remoção do material fotossensível não exposto. (4)Remoção e imediata recolocação de uma pequena lâmina da camada de SiO2 que assim fica superficialmente renovada e limpa. (5)Deposição de uma camada de material fotossensível. (6)Exposição desta camada à luz UV através de uma máscara que define as fontes e os drenos dos transístores nMOS. (7)Remoção do material fotossensível exposto. (8)Bombardeamento com átomos de Arsénio. Os átomos penetram através da camada mais fina de SiO2 mas são retidos e anulados pelas suas camadas mais espessas. O Arsénio nesta fase é preferível ao Fósforo por permitir maior concentração superficial e um perfil mais equilibrado.

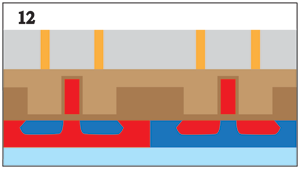

Quadro 12 – (1)Por um processo de recozimento a altas temperaturas, os átomos de Arsénio são adicionados à estrutura da Bolacha, criando assim as Fontes e os Drenos dos transístores nMOS. (2)Remoção do restante material fotossensível. (3)Remoção e reposição de uma pequena lâmina da camada de SiO2 que assim fica superficialmente renovada e limpa. (4)Deposição de nova camada de material fotossensível. (5)Sua exposição à luz UV através de uma máscara que define as fontes e os drenos dos transístores pMOS. (6)Remoção do material fotossensível exposto. (7)Bombardeamento com átomos de Boro. (8)Por um processo de recozimento a altas temperaturas, os átomos de Boro são adicionados à estrutura da Bolacha. Estão assim criadas as Fontes e os Drenos dos transístores pMOS. (9)Remoção de uma pequena lâmina da camada de SiO2. (10)Deposição de uma camada de SiO2 que deverá cobrir a totalidade dos componentes executados até agora, tendo uma função isolante relativamente às ligações metálicas que vamos começar a executar. (11)Deposição de uma camada de material fotossensível. (12)Sua exposição à luz UV através de uma máscara que define os contactos das fontes e drenos dos transístores.

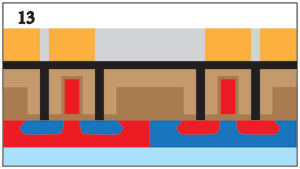

Quadro 13 – (1)Remoção do material fotossensível exposto. (2)Remoção por etching da camada exposta de SiO2, até ao silício dopado nos furos para os contactos com as fontes e drenos dos transístores. (3)Colocação de uma camada de metal condutor que vai preencher os furos abertos e estabelecer os contactos das fontes e drenos dos transístores. (4)Colocação de uma camada de material fotossensível. (5)Sua exposição à luz ultravioleta através de uma máscara que define o circuito elétrico ao nível desta camada.

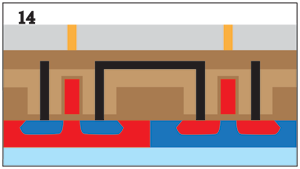

Quadro 14 – (1)Remoção do material fotossensível exposto. (2)Remoção por etching do material metálico agora exposto. (3)Remoção do material fotossensível sobrante. Fica assim definido o circuito elétrico que liga as fontes e drenos dos transístores nMOS e pMOS, interligando-os como CMOS e ligando os vários CMOS entre si. (4)Deposição de uma camada de SiO2 cobrindo a totalidade do circuito, que vai funcionar como isolante. (5)Deposição de uma camada de material fotossensível. (6)Sua Exposição à luz UV através de uma máscara que define os contactos com as portas dos transístores.

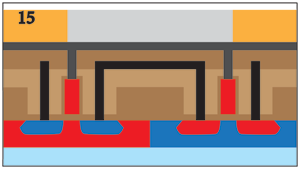

Quadro 15 – (1)Remoção do material fotossensível exposto. (2)Remoção por etching da camada de SiO2 exposta até ao polissílico n-dopado, nos furos para os contactos com as portas dos transístores. (3)Remoção do restante material fotossensível. (4)Deposição de uma camada de metal condutor, que vai preencher todos os orifícios de contactos com as portas. (5)Deposição de uma camada de material fotossensível sobre o metal. (6)Sua exposição à luz UV através de uma máscara que define o circuito elétrico das portas dos transístores.

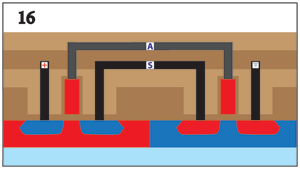

Quadro 16 – (1)Remoção do material fotossensível exposto. (2)Remoção por etching do material metálico agora exposto. (3)Remoção do material fotossensível sobrante. Fica assim definido o circuito elétrico que liga as portas dos agora já transístores CMOS . As ligações deste circuito estão a cinza para simbolizar que são executadas num plano diferente ao do corte em que estamos a trabalhar. (4)Deposição de uma camada de SiO2, com o fim de isolar e proteger os transístores e o eventual circuito em que estejam integrados.

A Lógica do CMOS

Os transístores CMOS são compostos sempre por dois transístores, sendo um NMOS e outro PMOS.

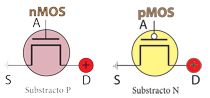

A representação gráfica de um transístor nMOS bem como a de um transístor pMOS é a que se pode ver na Figura 1.

Sendo VDD a sua tensão de alimentação:

Os transístores nMOS são condutores quando a sua porta é alimentada com tensão entre VDD/2 e VDD, equivalente ao valor lógico 1.

Os transístores pMOS são condutores quando a sua porta é alimentada com tensão entre 0 e VDD/2, equivalente ao valor lógico 0.

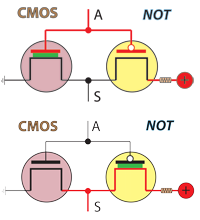

Os transístores CMOS constituem só por si um inversor, ou seja, uma porta NOT. Vamos perceber porquê, analisando a lógica do seu funcionamento.

A Figura 2 ilustra a representação gráfica de um transístor CMOS.

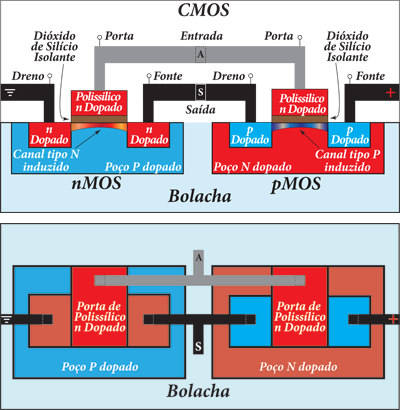

A Figura 3 pretende ser a transição entre o CMOS, tal com estará no silício e a sua representação gráfica e é apresentada em corte e em planta para que se possa entender como as ligações metálicas funcionam em diferentes planos.

Num transístor CMOS, a fonte do pMOS está ligada à alimentação e o dreno do nMOS à terra. O dreno do pMOS está ligado à fonte do nMOS e a saída S do CMOS está inserida nesta ligação. A entrada A está ligada a ambas as portas dos transístores nMOS e pMOS.

- Quando A tem o valor 1 , o nMOS é condutor e o pMOS isolante. Como a alimentação está ligada ao pMOS, não existirá corrente elétrica dentro do CMOS e a sua saída S terá o valor 0.

- Quando A tem o valor 0, o pMOS é condutor e o nMOS isolante. Portanto, a corrente elétrica entra no CMOS mas não se escoa para a terra através do nMOS. Logo, na ligação entre os dois transístores componentes, onde está ligada a saída S do CMOS, o valor é 1.

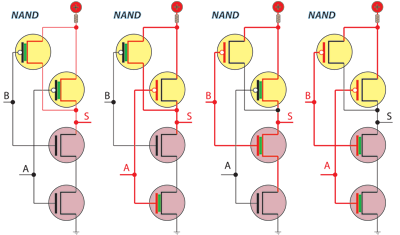

Porta NAND com CMOS

Como já vimos, o comportamento físico de uma porta lógica NAND foi conseguido pela ligação em série de dois transístores nMOS para o circuito aí representado.

No caso de transístores CMOS a questão já não é assim tão simples e, tal como dissemos, mais difícil de entender numa abordagem básica.

Pretendemos ter na saída o valor 1 sempre que uma ou ambas as entradas sejam 0.

Sempre que um transístor CMOS tiver um componente condutor o outro estará isolante. É através dos transístores pMOS que o CMOS está ligado à alimentação.

Como o pMOS é condutor com a porta a 0, o CMOS estará sempre alimentado desde que pelo menos uma das entradas esteja a 0, o que acontece se os dois pMOS estiverem ligados em paralelo à alimentação.

Para que esta situação se reflita na saída, é preciso que em nenhuma das situações anteriores a corrente elétrica se possa escoar para a terra.

Sempre que uma entrada for 0, um dos nMOS é condutor. Então os nMOS deverão estar ligados em série à terra. Desde que um deles esteja isolante a corrente elétrica já não se escoa. Se ambas as entradas forem 1 então o CMOS não está alimentado e a saída será 0.

Está encontrada a solução. Agora é preciso ligar os dois CMOS de forma que se cumpra o descrito, o que está refletido na Figura 4.

Assim podemos concluir que:

Para obter uma porta NAND com transístores CMOS colocam-se dois CMOS por forma a que:

- os dois nMOS fiquem em série na ligação à terra e

- os dois pMOS fiquem em paralelo na ligação à alimentação, isto é, ambos ligados individualmente à alimentação.

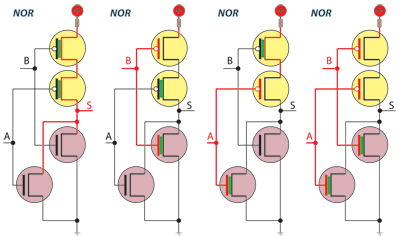

Porta NOR com CMOS

Pretendemos ter na saída sempre o valor lógico 0, exceto no caso em que ambas as entradas tenham esse valor lógico 0.

É através dos transístores pMOS que o CMOS está ligado à alimentação.

Como o pMOS é condutor com a porta a 0, o CMOS estará sempre alimentado desde que pelo menos uma das entradas esteja a 1. Tal só não acontece se os pMOS estiverem ligados em série à alimentação, bastando então que só um deles tenha a porta a 1 para o CMOS não estar alimentado.

Os transístores nMOS deverão sempre garantir ligação à terra quando o valor na saída for 0, para que esse estado não possa ser influenciado por qualquer ruído. Portanto deverão estar ligados à terra em paralelo, para que baste um deles ser condutor para garantir o escoamento de quaisquer tensões.

No caso das duas entradas a 0 ambos os pMOS são condutores e os nMOS isolantes, pelo que a saída será 1.

Está encontrada a solução. Agora é preciso ligar os dois CMOS de forma que se cumpra o descrito, o que está refletido na Figura 5.

Assim podemos concluir que:

Para obter uma porta NOR com transístores CMOS colocam-se dois transístores CMOS de forma a que:

- os NMOS fiquem ligados em paralelo à terra e que

- os PMOS fiquem ligados em série à alimentação.

Conclusão

Damos aqui por concluída esta parte sobre materialização das portas lógicas em circuitos elétricos.

Já percebemos que com os conceitos da álgebra booleana e com as portas lógicas tudo se pode resolver num computador. Já conseguimos materializar em circuitos elétricos o comportamento dessas portas. Já percebemos o que fazer com essa bicharada toda, a tal pergunta do final do Capitulo em que falámos dos bits.

Afinal, essa bicharada toda anda pelos circuitos do computador a ligar e desligar interruptores.

Simbolicamente, os bits, que são a unidade mínima de informação, através do seu estado de 1 ou 0, com tensão ou sem tensão, são enviados pelos circuitos do computador a ligar ou desligar interruptores (levar ou não tensão à Porta dos transístores) retornando com a resposta do circuito eletrónico que atravessam, ou fazendo o mesmo transporte para (OUT) circuitos externos ou de circuitos externos (IN).

E como é que isso faz operações aritméticas, põe imagens no ecrã e sons nas colunas?

Já lá vamos. Cada coisa a seu tempo.

Fixem bem aquilo que até agora verificaram. Todas as representações elétricas de portas lógicas foram feitas a partir dos circuitos NOT, NAND e NOR, como aliás fizemos questão de evidenciar.

Todos os circuitos que vamos estudar são formados por combinações das portas lógicas que tratámos. Portanto, combinações de NOT, NAND e NOR. Afinal é da mais elementar simplicidade, se descermos até à base e formos evoluindo por combinações daquilo que já aprendemos.

Complexa é a elaboração de raciocínios lógicos que nos permitam criar as combinações que resolvam os problemas que pretendemos.

Fundamental é perceber e interiorizar a funcionalidade de cada circuito, única forma de o podermos vir a incluir num raciocínio lógico futuro, isto é, num algoritmo mais complexo.

Na lógica matemática e na informática o limite é a nossa imaginação, como aliás se depreende da velocidade com que a computação progride a níveis nunca antes imaginados.

Vamos então perceber como é que o computador faz operações aritméticas.